ążąŠčĆčāą╝ ąĀą░ą┤ąĖąŠąÜąŠčé • ą¤čĆąŠčüą╝ąŠčéčĆ č鹥ą╝čŗ - stm32+AD9238. High-speed ADC. ąÜą░ąĮą░ą╗čŗ ąÉ ąĖ ąæ. ąØą░čüčéčĆąŠą╣ą║ą░ DMA

ąĪąŠąŠą▒čēąĄąĮąĖčÅ ą▒ąĄąĘ ąŠčéą▓ąĄč鹊ą▓ | ąÉą║čéąĖą▓ąĮčŗąĄ č鹥ą╝čŗ

ąĪčéčĆą░ąĮąĖčåą░ 1 ąĖąĘ 2

[ ąĪąŠąŠą▒čēąĄąĮąĖą╣: 31 ]

,

ąÉą▓č鹊čĆ

ąĪąŠąŠą▒čēąĄąĮąĖąĄ

dimaib

ąŚą░ą│ąŠą╗ąŠą▓ąŠą║ čüąŠąŠą▒čēąĄąĮąĖčÅ: stm32+AD9238. High-speed ADC. ąÜą░ąĮą░ą╗čŗ ąÉ ąĖ ąæ. ąØą░čüčéčĆąŠą╣ą║ą░ DMA

ąöąŠą▒ą░ą▓ą╗ąĄąĮąŠ: ą¦čé ą░ą▓ą│ 03, 2023 09:27:55

ą¤ąĄčĆą▓čŗą╣ čĆą░ąĘ čüą║ą░ąĘą░ą╗ ą£čÅčā!

ąŚą░čĆąĄą│ąĖčüčéčĆąĖčĆąŠą▓ą░ąĮ: ąĪą▒ ą░ą┐čĆ 02, 2011 04:05:00ąĪąŠąŠą▒čēąĄąĮąĖą╣: 33

ąĀąĄą╣čéąĖąĮą│ čüąŠąŠą▒čēąĄąĮąĖčÅ: 0

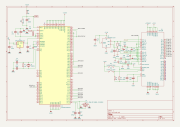

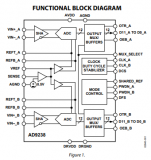

ąöąŠą▒čĆčŗą╣ ą┤ąĄąĮčī! ąśą╝ąĄąĄčéčüčÅ ąĘą░ą┤ą░čćą░, čćąĖčéą░čéčī čü ą┐ąŠą╝ąŠčēčīčÄ ą╝ąĖą║čĆąŠą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░ stm32h725vgt6, 12 ą▒ąĖčé čü ą┐ą░čĆą░ą╗ą╗ąĄą╗čīąĮąŠą╣ čłąĖąĮčŗ ą▓ąĮąĄčłąĮąĄą│ąŠ ąÉą”ą¤, ą┐čĆąĖ čćčæą╝ ą┤ą▓ą░ ąĄą│ąŠ ą║ą░ąĮą░ą╗ą░ ąÉ ąĖ ąæ ą▓ ą╝čāą╗čīčéąĖą┐ą╗ąĄą║čüąŠčĆąĮąŠą╝ čĆąĄąČąĖą╝ąĄ.

ą¦ą░čüč鹊čéą░ čéą░ą║čéąĖčĆąŠą▓ą░ąĮąĖčÅ ą┤ąŠą╗ąČąĮą░ ą▒čŗčéčī ąĮąĄ ą╝ąĄąĮąĄąĄ 4ą£ąōčå.

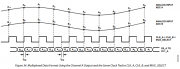

ąöą╗čÅ čĆąĄą░ą╗ąĖąĘą░čåąĖąĖ ą╝ąĄą╗čīčéąĖą┐ą╗ąĄą║čüąŠčĆąĮąŠą│ąŠ čĆąĄąČąĖą╝ą░, ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ ą┐ąĖąĮ MUX_SELECT. ąÜą░ą║ ąŠą┐ąĖčüą░ąĮąĮąŠ ą▓ ą┤ą░čéą░čłąĖč鹥, ąĄčüą╗ąĖ MUX_SELECT=0, č鹊 ąĮą░ ą▓čŗčģąŠą┤ąĮąŠą╣ 12 ą▒ąĖčéąĮąŠą╣ čłąĖąĮąĄ ą║ą░ąĮą░ą╗ą░ ąÉ, ą▒čāą┤čāčé ą┤ą░ąĮąĮčŗąĄ čü ą░ąĮą░ą╗ąŠą│ąŠą▓ąŠą│ąŠ ą║ą░ąĮą░ą╗ą░ ąæ, ą░ ąĮą░ čłąĖąĮąĄ ąæ ą▒čāą┤čāčé ą┤ą░ąĮąĮčŗąĄ čü ą░ąĮą░ą╗ąŠą│ąŠą▓ąŠą│ąŠ ą▓čģąŠą┤ą░ ąÉ. ąĢčüą╗ąĖ MUX_SELECT=1, č鹊 ąĮą░ ą▓čŗčģąŠą┤ąĮąŠą╣ čłąĖąĮąĄ ą║ą░ąĮą░ą╗ą░ ąÉ, ą▒čāą┤čāčé ą┤ą░ąĮąĮčŗąĄ čü ą░ąĮą░ą╗ąŠą│ąŠą▓ąŠą│ąŠ ą║ą░ąĮą░ą╗ą░ ąÉ, ą░ ąĮą░ čłąĖąĮąĄ ąæ ą▒čāą┤čāčé ą┤ą░ąĮąĮčŗąĄ čü ą░ąĮą░ą╗ąŠą│ąŠą▓ąŠą│ąŠ ą▓čģąŠą┤ą░ ąæ. ąŁč鹊 ą┐ąŠąĘą▓ąŠą╗čÅąĄčé ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčī č鹊ą╗čīą║ąŠ ąŠą┤ąĮčā čłąĖąĮčā ą┤ą░ąĮąĮčŗčģ ą┤ą╗čÅ čüčćąĖčéčŗą▓ą░ąĮąĖčÅ ą┤ą░ąĮąĮčŗčģ čü ą┤ą▓čāčģ ą║ą░ąĮą░ą╗ąŠą▓ ąÉą”ą¤.

ąØą░ čŹč鹊ą╝ ą│čĆą░čäąĖą║ąĄ ą▓ąĖą┤ąĮąŠ, čćč鹊 ąĄčüą╗ąĖ ąŠą▒čŖąĄą┤ąĖąĮąĖčéčī ą┐ąĖąĮčŗ čéą░ą║čéąĖčĆąŠą▓ą░ąĮąĖčÅ ą║ą░ąĮą░ą╗ąŠą▓ ąÉ, ąæ ąĖ MUX_SELECT, č鹊 ą╝ąŠąČąĮąŠ ąĘą░ ąŠą┤ąĖąĮ ą┐ąĄčĆąĄąŠą┤ čéą░ą║čéąĖčĆąŠą▓ą░ąĮąĖčÅ, čüčćąĖčéčŗą▓ą░čéčī ą┤ą▓ą░ ą║ą░ąĮą░ą╗ą░.

ąæą░čģ, ą▒ą░čģ, ą▒ą░čģ , ą▓čüčæ ą┤ąŠą╗ąČąĮąŠ čĆą░ą▒ąŠčéą░čéčī ą║ą░ą║ čćą░čüčŗ

, ąĮąŠ ąĮą░ ą┐čĆą░ą║čéąĖą║ąĄ ą▓čüčæ čüą╗ąŠąČąĮąĄąĄ..

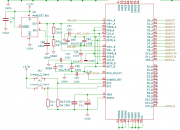

ąöą╗čÅ ą┐ą░čĆą░ą╗ą╗ąĄą╗čīąĮąŠą│ąŠ čüčćąĖčéčŗą▓ą░ąĮąĖčÅ 12 ą▒ąĖčé ąĮą░ ą▒ąŠą╗čīčłąŠą╣ čćą░čüč鹊č鹥 ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ DCMI ąĖ DMA. ąĢčüą╗ąĖ čćąĖčéą░čéčī č鹊ą╗čīą║ąŠ ąŠą┤ąĖąĮ ą║ą░ąĮą░ą╗ ąÉ ąĖą╗ąĖ ąæ, č鹊 ąĮąĖą║ą░ą║ąĖčģ ą┐čĆąŠą▒ą╗ąĄą╝ ąĮąĄ ą▓ąŠąĘąĮąĖą║ą░ąĄčé. ąöą░ąĮąĮčŗąĄ ą▒ąĄąĘ ą┐čĆąŠą▒ą╗ąĄą╝ ąĘą░ą│čĆčāąČą░čÄčéčüčÅ ą▓ ą╝ą░čüčüąĖą▓. ąĪčģąĄą╝ą░ ą┐ąŠą┤ą║ą╗čÄč湥ąĮąĖčÅ:

ąöą░ą╗ąĄąĄ čÅ ą┐čŗčéą░čÄčüčī čäąĖąĘąĖč湥čüą║ąĖ ą┐ąŠą┤ą║ą╗čÄčćąĖčéčī MUX_SELECT ą║ čéą░ą║čéąĖčĆąŠą▓ą░ąĮąĖčÄ ą║ą░ąĮą░ą╗ąŠą▓ ąÉ ąĖ ąæ. ąś ąŠąČąĖą┤ą░čÄ ąŠčé čŹč鹊ą│ąŠ, čćč鹊 ą▓ ą╝ą░čüčüąĖą▓ąĄ ą▓čüąĄ čćčæčéąĮčŗąĄ 菹╗ąĄą╝ąĄąĮčéčŗ ą▒čāą┤čāčé ą┤ą░ąĮąĮčŗąĄ čü ą║ą░ąĮą░ą╗ą░ ąÉ, ą░ ąĮąĄ čćčæčéąĮčŗąĄ, ą┤ą░ąĮąĮčŗąĄ čü ą║ą░ąĮą░ą╗ą░ ąæ. ąØąŠ ą┐ąŠą╗čāčćą░ąĄčéčüčÅ, čćč鹊 ą╝ą░čüčüąĖą▓ ąĘą░ą┐ąŠą╗ąĮąĄąĮ č鹊ą╗čīą║ąŠ ą┤ą░ąĮąĮčŗą╝ąĖ ą║ą░ąĮą░ą╗ą░ ąæ.

ą¤ąŠ čŹč鹊ą╝čā čüą┤ąĄą╗ą░ą╗ ą▓čŗą▓ąŠą┤, čćč鹊 DMA čüčćąĖčéčŗą▓ą░ąĄčé ą┤ą░ąĮąĮčŗąĄ ą▓ą║ąŠąĮčåąĄ ą┐ąĄčĆąĄąŠą┤ą░, ą║ą░ą║ ą┐ąŠą║ą░ąĘą░ą╗ ąĮą░ ą║ą░čĆčéąĖąĮą║ąĄ ąĮąĖąČąĄ:

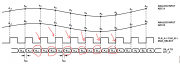

ą¤ąŠą┤čāą╝ą░ą╗, čćč鹊 ąĄčüą╗ąĖ čéą░ą║čéąĖčĆąŠą▓ą░čéčī ąÉą”ą¤ čćą░čüč鹊č鹊ą╣ ą┤ąĄą╗čæąĮąĮąŠą╣ ąĮą░ ą┤ą▓ą░, č鹊 DMA ą▒čāą┤ąĄčé čćąĖčéą░čéčī ą┤ą░ąĮąĮčŗąĄ ąĖ ą▓ ą┐ąĄčĆą▓ąŠą╣ ą┐ąŠą╗ąŠą▓ąĖąĮąĄ ą┐ąĄčĆąĄąŠą┤ą░ ąĖ ą▓ąŠ ą▓č鹊čĆąŠą╣. ąĪąŠą▒čĆą░ą╗ ą┤ąĄą╗ąĖč鹥ą╗čī čćą░čüč鹊čéčŗ ąĮą░ JK-čéčĆąĖą│ąĄčĆąĄ (čćč鹊 ą▒čŗą╗ąŠ ą┐ąŠą┤ čĆčāą║ąŠą╣), ąĖ ą┐ąŠą┤ą░ą╗ ąĮą░ ą▓čģąŠą┤ ą┤ąĄą╗ąĖč鹥ą╗čÅ čćą░čüč鹊čéčŗ, čüąĖą│ąĮą░ą╗ čü ą▓čŗčģąŠą┤ą░ ADC_CLKSRC (čŹč鹊čé čüąĖą│ąĮą░ą╗ čéčĆąĄą▒čāąĄčéčüčÅ ą┤ą╗čÅ ą▓ąĮąĄčłąĮąĄą│ąŠ čéą░ą║čéąĖčĆąŠą▓ą░ąĮąĖčÅ DCMI PIXCLK), ą░ ą║ ą▓čŗčģąŠą┤čā ą┤ąĄą╗ąĖč鹥ą╗čÅ, ą┐ąŠą┤ą║ą╗čÄčćąĖą╗ čéą░ą║čéąĖčĆąŠą▓ą░ąĮąĖąĄ ą║ą░ąĮą░ą╗ąŠą▓ ąÉ, ąæ ąĖ MUX_SELECT. ąĪčĆą░ą▓ąĮąĖą╗ ą┤ą▓ą░ čüąĖą│ąĮą░ą╗ą░, ą▓čģąŠą┤ąĮąŠą╣ ąĖ ą▓čŗčģąŠą┤ąĮąŠą╣, ą┤ą▓čāčģą║ą░ąĮą░ą╗čīąĮčŗą╝ ąŠčüčåąĖą╗ą╗ąŠą│čĆą░č乊ą╝, ą▓ąĖąČčā, čćč鹊 čćą░čüč鹊čéą░ ą┤ąĄą╣čüčéą▓ąĖč鹥ą╗čīąĮąŠ ą┤ąĄą╗ąĖčéčüčÅ ąĮą░ 2, ą▓ ąŠčüčéą░ą╗čīąĮąŠą╝ čüąĖą│ąĮą░ą╗čŗ ąĖą┤ąĄąĮčéąĖčćąĮčŗ. ąóą░ą║ąĖą╝ ąŠą▒čĆą░ąĘąŠą╝ čćą░čüč鹊čéą░ čüąĖą│ąĮą░ą╗ą░ ąĮą░ PIXCLK ąŠčüčéą░ą╗ą░čüčī ą┐čĆąĄąČąĮąĄą╣, ą░ ąÉą”ą¤, čéą░ą║čéąĖčĆčāąĄčéčüčÅ ą╝ąĄąĮčīčłąĄą╣ čćą░čüč鹊č鹊ą╣. ąÆ ąĖč鹊ą│ąĄ ą┐ąŠą╗čāčćą░čÄ ą┐ąŠčćčéąĖ ą▓ąĄčüčī ą╝ą░čüčüąĖą▓ ąĘą░ą┐ąŠą╗ąĮąĄąĮčŗą╣ ą┤ą░ąĮąĮčŗą╝ąĖ čü ą║ą░ąĮą░ą╗ą░ ąÉ, ąĖ ąŠč湥ąĮčī čĆąĄą┤ą║ąŠ ą▓ ą╝ą░čüčüąĖą▓ąĄ ą▓čüčéčĆąĄčćą░čÄčéčüčÅ ą┤ą░ąĮąĮčŗąĄ čü ą║ą░ąĮą░ą╗ą░ ąæ.

ą¤ąŠą┤čüą║ą░ąČąĖč鹥, ą┐ąŠąČą░ą╗čāą╣čüčéą░, ą║ą░ą║ ą┐čĆą░ą▓ąĖą╗čīąĮąŠ ąĮą░čüčéčĆąŠąĖčéčī, ą┤ą╗čÅ ą╝ąŠąĄą│ąŠ čüą╗čāčćą░čÅ, DMA? ą» čéą░ą║ ąČąĄ ą┐čĆąŠą▒ąŠą▓ą░ą╗ ąĖąĘą╝ąĄąĮčÅčéčī ąĮąĄą║ąŠč鹊čĆčŗąĄ ąĮą░čüčéčĆąŠą╣ą║ąĖ, ąĮąŠ čŹč鹊 ą┐ą░ą╗čīčåąĄą╝ ą▓ ąĮąĄą▒ąŠ, ąĖ čĆąĄąĘčāą╗čīčéą░č鹊ą▓ ąĮąĄ ą┐čĆąĖąĮąĄčüą╗ąŠ! ą» ą┐ąŠąĮąĖą╝ą░čÄ, čćč鹊 ą┐čĆąŠą▒ą╗ąĄą╝ą░ ą▓ čüąĖąĮčģčĆąŠąĮąĖąĘą░čåąĖąĖ ą╝ąĄąČą┤čā čéą░ą║čéąĖčĆąŠą▓ą░ąĮąĖąĄą╝ DCMI ąĖ čéą░ą║čéąĖčĆąŠą▓ą░ąĮąĖąĄą╝ ąÉą”ą¤, ąĮąŠ ąĮąĄ ąĘąĮą░čÄ ą║ą░ą║ čŹč鹊 ąĖčüą┐čĆą░ą▓ąĖčéčī.

ąÆąŠčé ą╝ąŠąĖ ąĮą░čüčéčĆąŠą╣ą║ąĖ DMA, DCMI ąĖ ą║ą░ąĮą░ą╗ąŠą▓ čéą░ą╣ą╝ąĄčĆąŠą▓ ą┤ą╗čÅ čéą░ą║čéąĖčĆąŠą▓ą░ąĮąĖčÅ. ąÜąŠąĮčéčĆąŠą╗ą╗ąĄčĆ čĆą░ą▒ąŠčéą░ąĄčé ąĮą░ čćą░čüč鹊č鹥 550ą£ąōčå.

ąśąĮąĖčåąĖą░ą╗ąĖąĘą░čåąĖčÅ GPIO: ąÜąŠą┤:

static void hw_dcmi_gpio_init ( void )

ąśąĮąĖčåąĖą░ą╗ąĖąĘą░čåąĖčÅ čéą░ą╣ą╝ąĄčĆąŠą▓ ąĖ čéą░ą║čéąĖčĆąŠą▓ą░ąĮąĖčÅ: ąÜąŠą┤:

static void hw_adc_clksrc_init ( void )

ąśąĮąĖčåąĖą░ą╗ąĖąĘą░čåąĖčÅ DMA: ąÜąŠą┤:

static void hw_dcmi_dma_init ( void )

ąśąĘą▓ąĖąĮąĖč鹥, ąĄčüą╗ąĖ ą┤ą░ą╗ ąĮąĄ ą┐ąŠą╗ąĮčāčÄ ąĖąĮč乊čĆą╝ą░čåąĖčÄ, ą│ąŠč鹊ą▓ ą┐čĆąĄą┤ąŠčüčéą░ą▓ąĖčéčī ą▓čüčæ čćč鹊 ą┐ąŠčéčĆąĄą▒čāąĄčéčüčÅ! ą» ą┐ąŠąĮąĖą╝ą░čÄ, čćč鹊 ąŠą┐čéąĖą╝ą░ą╗čīąĮąŠąĄ čĆąĄčłąĄąĮąĖąĄ ą┤ą╗čÅ ą┤ą░ąĮąĮąŠą╣ ąĘą░ą┤ą░čćąĖ ą▒čāą┤ąĄčé ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĖąĄ FPGA, ąĮąŠ ą┤ą░ąĮčŗą╣ ą┐čĆąŠąĄą║čé čāąČąĄ ąĖą╝ąĄąĄčé čĆąĄą░ą╗ąĖąĘą░čåąĖčÄ ąĮą░ stm32 ąĖ čéčĆąĄą▒čāąĄčé ą╝ąĖąĮąĖą╝ą░ą╗čīąĮčŗčģ ąĖąĘą╝ąĄąĮąĄąĮąĖą╣ ą▓ čüčģąĄą╝ąĄ ąĖ ą┐ąĄčćą░čéąĮąŠą╣ ą┐ą╗ą░č鹥. ąöą░ ąĖ FPGA čÅ ąĮąĄ ą▓ą╗ą░ą┤ąĄčÄ

ąśčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĖąĄ HAL čéą░ą║ ąČąĄ ą┤ąĖą║čéčāąĄčéčüčÅ čāčüą╗ąŠą▓ąĖčÅą╝ąĖ ą┐čĆąŠąĄą║čéą░.

ąĪą┐ą░čüąĖą▒ąŠ!

ąÆąĄčĆąĮčāčéčīčüčÅ ąĮą░ą▓ąĄčĆčģ

ąĀąĄą║ą╗ą░ą╝ą░

>TEHb<

ąŚą░ą│ąŠą╗ąŠą▓ąŠą║ čüąŠąŠą▒čēąĄąĮąĖčÅ: Re: stm32+AD9238. High-speed ADC. ąÜą░ąĮą░ą╗čŗ ąÉ ąĖ ąæ. ąØą░čüčéčĆąŠą╣ą║ą░ DM

ąöąŠą▒ą░ą▓ą╗ąĄąĮąŠ: ą¦čé ą░ą▓ą│ 03, 2023 09:42:05

ąöčĆčāą│ ąÜąŠčéą░

ąÜą░čĆą╝ą░: 13

ąĀąĄą╣čéąĖąĮą│ čüąŠąŠą▒čēąĄąĮąĖą╣: 359

ąŚą░čĆąĄą│ąĖčüčéčĆąĖčĆąŠą▓ą░ąĮ: ąĪčĆ ąĮąŠčÅ 11, 2009 17:19:30ąĪąŠąŠą▒čēąĄąĮąĖą╣: 4323ą×čéą║čāą┤ą░: ąÆąŠčĆąŠąĮąĄąČ

ąĀąĄą╣čéąĖąĮą│ čüąŠąŠą▒čēąĄąĮąĖčÅ: 0

ąĢčüą╗ąĖ čÅ ą┐čĆą░ą▓ąĖą╗čīąĮąŠ ą┐ąŠąĮčÅą╗ čüąĖčéčāą░čåąĖčÄ, č鹊 čćąĖčéą░čéčī čüč鹊ąĖčé ą▓ čüąĄčĆąĄą┤ąĖąĮąĄ ąĖą╝ą┐čāą╗čīčüą░ čéą░ą║čéąĖčĆąŠą▓ą░ąĮąĖčÅ, ą░ ąĮąĄ ąĮą░ čäčĆąŠąĮč鹥 ą┐ąĄčĆąĄą┤ąĮąĄą╝ ąĖą╗ąĖ ąĘą░ą┤ąĮąĄą╝. ąóąŠą╗ąĖ ą╝ąĖą║čĆčāčģą░ čāčüą┐ąĄąĄčé ą▓čŗčüčéą░ą▓ąĖčéčī ąĘąĮą░č湥ąĮąĖąĄ, č鹊ą╗ąĖ ąĮąĄčé. ąóąŠ ąĄčüčéčī čüč鹊ąĖčé ąĮąĄ čćą░čüč鹊čéčā čüąĮąĖąČą░čéčī, ą░ čäą░ąĘčā ą┤ą▓ąĖą│ą░čéčī.

ąÆąĄčĆąĮčāčéčīčüčÅ ąĮą░ą▓ąĄčĆčģ

ąĀąĄą║ą╗ą░ą╝ą░

dimaib

ąŚą░ą│ąŠą╗ąŠą▓ąŠą║ čüąŠąŠą▒čēąĄąĮąĖčÅ: Re: stm32+AD9238. High-speed ADC. ąÜą░ąĮą░ą╗čŗ ąÉ ąĖ ąæ. ąØą░čüčéčĆąŠą╣ą║ą░ DM

ąöąŠą▒ą░ą▓ą╗ąĄąĮąŠ: ą¦čé ą░ą▓ą│ 03, 2023 09:56:19

ą¤ąĄčĆą▓čŗą╣ čĆą░ąĘ čüą║ą░ąĘą░ą╗ ą£čÅčā!

ąŚą░čĆąĄą│ąĖčüčéčĆąĖčĆąŠą▓ą░ąĮ: ąĪą▒ ą░ą┐čĆ 02, 2011 04:05:00ąĪąŠąŠą▒čēąĄąĮąĖą╣: 33

ąĀąĄą╣čéąĖąĮą│ čüąŠąŠą▒čēąĄąĮąĖčÅ: 0

ąóąŠąĄčüčéčī ą▓čŗ čģąŠčéąĖč鹥 čüą║ą░ąĘą░čéčī, čćč鹊 ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĖąĄ ą┤ąĄą╗ąĖč鹥ą╗čÅ čćą░čüč鹊čéčŗ ąĮąĄ ą▓ąĄčĆąĮąŠ? ą£ąĮąĄ čüč鹊ąĖčé čéą░ą║čéąĖčĆąŠą▓ą░čéčī ąÉą”ą¤, č鹊ą╣ ąČąĄ čćą░čüč鹊č鹊ą╣, čćč鹊 ąĖ DCMI? ąóąŠą╗čīą║ąŠ ą║ ą┐čĆąĖą╝ąĄčĆčā ąĮą░čüčéčĆąŠąĖčéčī ąĄčēčæ ąŠą┤ąĖąĮ čéą░ą╣ą╝ąĄčĆ ąĮą░ čéčāąČąĄ čćą░čüč鹊čéčā ąĖ ąĘą░ą┐čāčüą║ą░čéčī ąĄą│ąŠ čü ąĮąĄą║ąŠč鹊čĆąŠą╣ ąĘą░ą┤ąĄčƹȹ║ąŠą╣ ąŠčé čéą░ą╣ą╝ąĄčĆą░ čéą░ą║čéąĖčĆčāčÄčēąĄą│ąŠ DCMI? ąÆąĄčĆąĮąŠ?

ąÆąĄčĆąĮčāčéčīčüčÅ ąĮą░ą▓ąĄčĆčģ

ąĀąĄą║ą╗ą░ą╝ą░

>TEHb<

ąŚą░ą│ąŠą╗ąŠą▓ąŠą║ čüąŠąŠą▒čēąĄąĮąĖčÅ: Re: stm32+AD9238. High-speed ADC. ąÜą░ąĮą░ą╗čŗ ąÉ ąĖ ąæ. ąØą░čüčéčĆąŠą╣ą║ą░ DM

ąöąŠą▒ą░ą▓ą╗ąĄąĮąŠ: ą¦čé ą░ą▓ą│ 03, 2023 10:08:48

ąöčĆčāą│ ąÜąŠčéą░

ąÜą░čĆą╝ą░: 13

ąĀąĄą╣čéąĖąĮą│ čüąŠąŠą▒čēąĄąĮąĖą╣: 359

ąŚą░čĆąĄą│ąĖčüčéčĆąĖčĆąŠą▓ą░ąĮ: ąĪčĆ ąĮąŠčÅ 11, 2009 17:19:30ąĪąŠąŠą▒čēąĄąĮąĖą╣: 4323ą×čéą║čāą┤ą░: ąÆąŠčĆąŠąĮąĄąČ

ąĀąĄą╣čéąĖąĮą│ čüąŠąŠą▒čēąĄąĮąĖčÅ: 0

ąĪ čŹčéąĖą╝ ąÉą”ą¤ ąĮąĄ čĆą░ą▒ąŠčéą░ą╗, čéą░ą║ čćč鹊 ąĮą░ą▓ąĄčĆąĮčÅą║ą░ ąĮąĄ čüą║ą░ąČčā. ą¤ąŠčüą╝ąŠčéčĆąĖč鹥 ą▓ ą║ą░ą║ąŠą╣ ą╝ąŠą╝ąĄąĮčé ąĖąĮč鹥čĆč乥ą╣čü ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░ ą┐čĆąŠąĖąĘą▓ąŠą┤ąĖčé ą▓čŗą▒ąŠčĆą║čā ą┤ą░ąĮąĮčŗčģ čü ą╗ąĖąĮąĖąĖ ąĖ ą▓ ą║ą░ą║ąŠą╣ ą╝ąŠą╝ąĄąĮčé ąÉą”ą¤ ą▓čŗčüčéą░ą▓ą╗čÅąĄčé ąĮčāąČąĮčŗąĄ čāčĆąŠą▓ąĮąĖ. ąØąĄąŠą▒čģąŠą┤ąĖą╝ąŠ čüą┤ąĄą╗ą░čéčī čéą░ą║, čćč鹊ą▒čŗ ą▓ ą╝ąŠą╝ąĄąĮčé čüčćąĖčéčŗą▓ą░ąĮąĖčÅ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░č鹥ą╗čī ą│ą░čĆą░ąĮčéąĖčĆąŠą▓ą░ąĮąĮąŠ čāčüčéą░ąĮąŠą▓ąĖą╗ ąĮą░ čłąĖąĮąĄ ąĮčāąČąĮčŗąĄ ą┤ą░ąĮąĮčŗąĄ, ą▓ čŹč鹊ą╝ čüą╝čŗčüą╗.

ąÆąĄčĆąĮčāčéčīčüčÅ ąĮą░ą▓ąĄčĆčģ

ąĀąĄą║ą╗ą░ą╝ą░

ąÆčŗą▒ąĖčĆą░ąĄą╝ čüčģąĄą╝čā BMS ą┤ą╗čÅ ąĘą░čĆčÅą┤ą░ ą╗ąĖčéąĖą╣-ąČąĄą╗ąĄąĘąŠč乊čüčäą░čéąĮčŗčģ (LiFePO4) ą░ą║ą║čāą╝čāą╗čÅč鹊čĆąŠą▓

ą×ą▒čÅąĘą░č鹥ą╗čīąĮčŗą╝ čāčüą╗ąŠą▓ąĖąĄą╝ ą┤ąŠą╗ą│ąŠą╣ ąĖ čüčéą░ą▒ąĖą╗čīąĮąŠą╣ čĆą░ą▒ąŠčéčŗ Li-FePO4-ą░ą║ą║čāą╝čāą╗čÅč鹊čĆąŠą▓, ą▓ č鹊ą╝ čćąĖčüą╗ąĄ ąĖ ą┐čĆąŠąĖąĘą▓ąŠą┤čüčéą▓ą░ EVE Energy, čÅą▓ą╗čÅąĄčéčüčÅ ą┐čĆąĖą╝ąĄąĮąĄąĮąĖąĄ čüą┐ąĄčåąĖą░ą╗ąĖąĘąĖčĆąŠą▓ą░ąĮąĮčŗčģ BMS-ą╝ąĖą║čĆąŠčüčģąĄą╝. ąøąĖčéąĖą╣-ąČąĄą╗ąĄąĘąŠč乊čüčäą░čéąĮčŗąĄ ąÉąÜąæ ąŠčéą╗ąĖčćą░čÄčéčüčÅ čéą░ą║ąĖą╝ąĖ čģą░čĆą░ą║č鹥čĆąĖčüčéąĖą║ą░ą╝ąĖ, ą║ą░ą║ ą▓čŗčüąŠą║ą░čÅ ą╝ąĮąŠą│ąŠą║čĆą░čéąĮąŠčüčéčī čåąĖą║ą╗ąŠą▓ ąĘą░čĆčÅą┤ą░-čĆą░ąĘčĆčÅą┤ą░, ą▒ąĄąĘąŠą┐ą░čüąĮąŠčüčéčī, ą▓ąŠąĘą╝ąŠąČąĮąŠčüčéčī ą▒čŗčüčéčĆąŠą╣ ąĘą░čĆčÅą┤ą║ąĖ, čāčüč鹊ą╣čćąĖą▓ąŠčüčéčī ą║ ą▒čāč乥čĆąĮąŠą╝čā čĆąĄąČąĖą╝čā čĆą░ą▒ąŠčéčŗ ąĖ ą┐čĆąĖąĄą╝ą╗ąĄą╝ą░čÅ čüč鹊ąĖą╝ąŠčüčéčī. ąØąŠ ą┤ą╗čÅ čŹčéąĖčģ ąÉąÜąæ ąŠč湥ąĮčī ą▓ą░ąČąĄąĮ ą║ąŠąĮčéčĆąŠą╗čī ą┐čĆąŠčåąĄčüčüą░ ąĘą░čĆčÅą┤ą░ ąĖ čĆą░ąĘčĆčÅą┤ą░ ą┤ą╗čÅ ąĖąĘą▒ąĄą│ą░ąĮąĖčÅ ą▓ąŠąĘą┤ąĄą╣čüčéą▓ąĖčÅ ą▓ąĮąĄčłąĮąĄą│ąŠ ąĘą░čĆčÅą┤ąĮąŠą│ąŠ ąĮą░ą┐čĆčÅąČąĄąĮąĖčÅ ą┐ąŠčüą╗ąĄ ą┤ąŠčüčéąĖąČąĄąĮąĖčÅ 100% ąĘą░čĆčÅą┤ą░. ąśąĮąČąĄąĮąĄčĆčŗ ąÜą×ą£ą¤ąŁąø ą┐ąŠą┤ą│ąŠč鹊ą▓ąĖą╗ąĖ čüą┐ąĖčüąŠą║ čéą░ą║ąĖčģ čĆąĄčłąĄąĮąĖą╣ ąŠčé čĆą░ąĘąĮčŗčģ ą┐čĆąŠąĖąĘą▓ąŠą┤ąĖč鹥ą╗ąĄą╣.

ą¤ąŠą┤čĆąŠą▒ąĮąĄąĄ>>

dimaib

ąŚą░ą│ąŠą╗ąŠą▓ąŠą║ čüąŠąŠą▒čēąĄąĮąĖčÅ: Re: stm32+AD9238. High-speed ADC. ąÜą░ąĮą░ą╗čŗ ąÉ ąĖ ąæ. ąØą░čüčéčĆąŠą╣ą║ą░ DM

ąöąŠą▒ą░ą▓ą╗ąĄąĮąŠ: ą¦čé ą░ą▓ą│ 03, 2023 19:13:10

ą¤ąĄčĆą▓čŗą╣ čĆą░ąĘ čüą║ą░ąĘą░ą╗ ą£čÅčā!

ąŚą░čĆąĄą│ąĖčüčéčĆąĖčĆąŠą▓ą░ąĮ: ąĪą▒ ą░ą┐čĆ 02, 2011 04:05:00ąĪąŠąŠą▒čēąĄąĮąĖą╣: 33

ąĀąĄą╣čéąĖąĮą│ čüąŠąŠą▒čēąĄąĮąĖčÅ: 0

ąØą░čćąĮčā čü ą║ąŠąĮčåą░)

ą”ąĖčéą░čéą░:

ąĢčüą╗ąĖ ą│ą╗ąŠą▒ą░ą╗čīąĮąŠ, č鹊 ąĘą░č湥ą╝ ą▓ąŠąŠą▒čēąĄ ą▓ąĮąĄčłąĮąĖą╣ ąÉą”ą¤? ąóą░ą╝ ąĖ ą▓ąĮčāčéčĆąĄąĮąĮąĖą╣ ą╝ąĮąŠą│ąĖą╝ ą┤ą░čüčé ą┐čĆąĖą║čāčĆąĖčéčī.

ąÜą░ą║ čÅ ą│ąŠą▓ąŠčĆąĖą╗ ą▓ąĮą░čćą░ą╗ąĄ, ą┤ą░ąĮąĮčŗąĄ čéčĆąĄą▒čāąĄčéčüčÅ čüčćąĖčéčŗą▓ą░čéčī čü čćą░čüč鹊č鹊ą╣ ąĮąĄ ą╝ąĄąĮąĄąĄ 4ą£ąōčå, ąĮąŠ ą▓ ą┐ąĄčĆčüą┐ąĄą║čéąĖą▓ąĄ, č湥ą╝ ą▒ąŠą╗čīčłąĄ čćą░čüč鹊čéą░, č鹥ą╝ ą╗čāčćčłąĄ. ąÉ ą┤ą░ąĮąĮčŗą╣ ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆ ą▒ąŠą╗čīčłąĄ 3-4MSPS ąĮąĄ ą▓čŗą┤ą░čüčé.

ą”ąĖčéą░čéą░:

ąØąĄąŠą▒čģąŠą┤ąĖą╝ąŠ čüą┤ąĄą╗ą░čéčī čéą░ą║, čćč鹊ą▒čŗ ą▓ ą╝ąŠą╝ąĄąĮčé čüčćąĖčéčŗą▓ą░ąĮąĖčÅ ą┐čĆąĄąŠą▒čĆą░ąĘąŠą▓ą░č鹥ą╗čī ą│ą░čĆą░ąĮčéąĖčĆąŠą▓ą░ąĮąĮąŠ čāčüčéą░ąĮąŠą▓ąĖą╗ ąĮą░ čłąĖąĮąĄ ąĮčāąČąĮčŗąĄ ą┤ą░ąĮąĮčŗąĄ, ą▓ čŹč鹊ą╝ čüą╝čŗčüą╗.

ąöą░! ąŁč鹊 čÅ ą┐ąŠąĮčÅą╗! ąØą░ą┤ąĄčÄčüčī ą┐čĆąŠą▒ą╗ąĄą╝ą░ ą▓ čŹč鹊ą╝.. ąæčāą┤čā č鹥čüčéąĖčĆąŠą▓ą░čéčī

ą”ąĖčéą░čéą░:

ą¤ąŠčüą╝ąŠčéčĆąĖč鹥 ą▓ ą║ą░ą║ąŠą╣ ą╝ąŠą╝ąĄąĮčé ąĖąĮč鹥čĆč乥ą╣čü ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░ ą┐čĆąŠąĖąĘą▓ąŠą┤ąĖčé ą▓čŗą▒ąŠčĆą║čā ą┤ą░ąĮąĮčŗčģ čü ą╗ąĖąĮąĖąĖ ąĖ ą▓ ą║ą░ą║ąŠą╣ ą╝ąŠą╝ąĄąĮčé ąÉą”ą¤ ą▓čŗčüčéą░ą▓ą╗čÅąĄčé ąĮčāąČąĮčŗąĄ čāčĆąŠą▓ąĮąĖ.

ąöą░, čŹč鹊 ą╗ąŠą│ąĖčćąĮčŗąĄ čłą░ą│ąĖ! ąØąŠ ą║ą░ą║ čŹč鹊 čüą┤ąĄą╗ą░čéčī? ą» ąĮąĄ ą┐čĆąĄą┤čüčéą░ą▓ą╗čÅčÄ ą║ą░ą║ ąĘą░čäąĖą║čüąĖčĆąŠą▓ą░čéčī ą╝ąŠą╝ąĄąĮčé ą▓čŗą▒ąŠčĆą║ąĖ ą┤ą░ąĮąĮčŗčģ, ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣ ąĮą░ čŹč鹊čé čüą╗čāčćą░ą╣ ąĮąĄčé.

ą» čģąŠčćčā ą┐ąŠą┐čĆąŠą▒ąŠą▓ą░čéčī ąĮą░čüčéčĆąŠąĖčéčī čüč鹊čĆąŠąĮąĮąĖą╣ čéą░ą╣ą╝ąĄčĆ ąĖ ąĘą░ą┐čāčüčéąĖčéčī ąĄą│ąŠ čüąŠ čüą╝ąĄčēąĄąĮąĖąĄą╝ ą┐ąŠ ą▓čĆąĄą╝ąĄąĮąĖ. ąØąŠ ą▒čāą┤čā ąČą┤ą░čéčī ą┤čĆčāą│ąĖčģ čüąŠą▓ąĄč鹊ą▓!

ąÆąĄčĆąĮčāčéčīčüčÅ ąĮą░ą▓ąĄčĆčģ

ąĀąĄą║ą╗ą░ą╝ą░

ąĀąĄą║ą╗ą░ą╝ą░

ąØąŠą▓čŗą╣ ą░ą║ą║čāą╝čāą╗čÅč鹊čĆ EVE čüąĄčĆąĖąĖ PLM ą┤ą╗čÅ GSM-čéčĆąĄą║ąĄčĆąŠą▓, čĆą░ą▒ąŠčéą░čÄčēąĖčģ ą▓ ąČčæčüčéą║ąĖčģ čāčüą╗ąŠą▓ąĖčÅčģ (ą┤ąŠ -40┬░ąĪ)

ąÜąŠą╝ą┐ą░ąĮąĖčÅ EVE ą▓čŗą┐čāčüčéąĖą╗ą░ ąĮąŠą▓čŗą╣ ą░ą║ą║čāą╝čāą╗čÅč鹊čĆ čüąĄčĆąĖąĖ PLM, čüąŠč湥čéą░čÄčēąĖą╣ ą▓ čüąĄą▒ąĄ ą▓čŗčüąŠą║čāčÄ ą▒ąĄąĘąŠą┐ą░čüąĮąŠčüčéčī, ą┤ą╗ąĖč鹥ą╗čīąĮčŗą╣ čüčĆąŠą║ čüą╗čāąČą▒čŗ, čłąĖčĆąŠą║ąĖą╣ č鹥ą╝ą┐ąĄčĆą░čéčāčĆąĮčŗą╣ ą┤ąĖą░ą┐ą░ąĘąŠąĮ ąĖ ą▓čŗčüąŠą║čāčÄ č鹊ą║ąŠąŠčéą┤ą░čćčā ą┤ą░ąČąĄ ą┐čĆąĖ ąŠčéčĆąĖčåą░č鹥ą╗čīąĮąŠą╣ č鹥ą╝ą┐ąĄčĆą░čéčāčĆąĄ.

ąŁčéąĖ ą░ą║ą║čāą╝čāą╗čÅč鹊čĆčŗ ą┐ąŠą┤ą┤ąĄčƹȹĖą▓ą░čÄčé ąĘą░čĆčÅą┤ ą┐čĆąĖ č鹥ą╝ą┐ąĄčĆą░čéčāčĆąĄ ąŠčé -40/-20┬░ąĪ (čüąĮąĖąČąĄąĮąĮčŗą╝ ąĘąĮą░č湥ąĮąĖąĄą╝ č鹊ą║ą░), ą▒ąĄąĘąŠą┐ą░čüąĮčŗ (ąĮąĄ ą▓ąŠčüą┐ą╗ą░ą╝ąĄąĮčÅčÄčéčüčÅ ąĖ ąĮąĄ ą▓ąĘčĆčŗą▓ą░čÄčéčüčÅ) ą┐čĆąĖ ą╝ąĄčģą░ąĮąĖč湥čüą║ąŠą╝ ą┐ąŠą▓čĆąĄąČą┤ąĄąĮąĖąĖ (ą┐čĆąŠčéčŗą║ą░ąĮąĖąĄ ąĖ čüą┤ą░ą▓ą╗ąĖą▓ą░ąĮąĖąĄ), čāčüč鹊ą╣čćąĖą▓čŗ ą║ ą▓ąĖą▒čĆą░čåąĖąĖ. ą×ąĮąĖ ą╝ąŠą│čāčé ą┐čĆąĖą╝ąĄąĮčÅčéčīčüčÅ ą║ą░ą║ ą┤ą╗čÅ ą░ą▓č鹊čéčĆą░ąĮčüą┐ąŠčĆčéą░ (čéčĆąĄą║ąĄčĆčŗ, ą╝ą░čÅčćą║ąĖ, čüąĖą│ąĮą░ą╗ąĖąĘą░čåąĖčÅ), čéą░ą║ ąĖ ą┤ą╗čÅ ą┐čĆąŠą╝čŗčłą╗ąĄąĮąĮčŗčģ čāčüčéčĆąŠą╣čüčéą▓ ą╝ąŠąĮąĖč鹊čĆąĖąĮą│ą░, IoT-čāčüčéčĆąŠą╣čüčéą▓.

ą¤ąŠą┤čĆąŠą▒ąĮąĄąĄ>>

GARMIN

ąŚą░ą│ąŠą╗ąŠą▓ąŠą║ čüąŠąŠą▒čēąĄąĮąĖčÅ: Re: stm32+AD9238. High-speed ADC. ąÜą░ąĮą░ą╗čŗ ąÉ ąĖ ąæ. ąØą░čüčéčĆąŠą╣ą║ą░ DM

ąöąŠą▒ą░ą▓ą╗ąĄąĮąŠ: ą¦čé ą░ą▓ą│ 03, 2023 20:19:30

ą×ą┐čŗčéąĮčŗą╣ ą║ąŠčé

ąÜą░čĆą╝ą░: 16

ąĀąĄą╣čéąĖąĮą│ čüąŠąŠą▒čēąĄąĮąĖą╣: 170

ąŚą░čĆąĄą│ąĖčüčéčĆąĖčĆąŠą▓ą░ąĮ: ąÆčü ą┤ąĄą║ 02, 2012 16:58:33ąĪąŠąŠą▒čēąĄąĮąĖą╣: 829ą×čéą║čāą┤ą░: ąŻąČąĄ ąĮąĄ ą│ąŠčĆąŠą┤ ąæąĄą╗čŗčģ ą│ąŠčĆ

ąĀąĄą╣čéąĖąĮą│ čüąŠąŠą▒čēąĄąĮąĖčÅ: 0

ąśąĮą▓ąĄčĆč鹊čĆ čéą░ą║č鹊ą▓ąŠą│ąŠ čüąĖą│ąĮą░ą╗ą░!

ąÆąĄčĆąĮčāčéčīčüčÅ ąĮą░ą▓ąĄčĆčģ

ąĀąĄą║ą╗ą░ą╝ą░

dimaib

ąŚą░ą│ąŠą╗ąŠą▓ąŠą║ čüąŠąŠą▒čēąĄąĮąĖčÅ: Re: stm32+AD9238. High-speed ADC. ąÜą░ąĮą░ą╗čŗ ąÉ ąĖ ąæ. ąØą░čüčéčĆąŠą╣ą║ą░ DM

ąöąŠą▒ą░ą▓ą╗ąĄąĮąŠ: ą¦čé ą░ą▓ą│ 03, 2023 20:23:01

ą¤ąĄčĆą▓čŗą╣ čĆą░ąĘ čüą║ą░ąĘą░ą╗ ą£čÅčā!

ąŚą░čĆąĄą│ąĖčüčéčĆąĖčĆąŠą▓ą░ąĮ: ąĪą▒ ą░ą┐čĆ 02, 2011 04:05:00ąĪąŠąŠą▒čēąĄąĮąĖą╣: 33

ąĀąĄą╣čéąĖąĮą│ čüąŠąŠą▒čēąĄąĮąĖčÅ: 0

ąöą░, čÅ ą┐čĆąŠą▒ąŠą▓ą░ą╗ ą▒čĆą░čéčī čéą░ą║č鹊ą▓čŗą╣ čüąĖą│ąĮą░ą╗ ąĮąĄ čü ą┐čĆčÅą╝ąŠą│ąŠ ą▓čŗčģąŠą┤ą░ Q, ą┤ąĄą╗ąĖč鹥ą╗čÅ, ą░ čü ąĖąĮą▓ąĄčĆčéąĮąŠą│ąŠ, čüąĖčéčāą░čåąĖčÅ čüąŠčģčĆą░ąĮčÅąĄčéčüčÅ ą┐čĆąĄąČąĮąĄą╣.

ąÆąĄčĆąĮčāčéčīčüčÅ ąĮą░ą▓ąĄčĆčģ

ąĀąĄą║ą╗ą░ą╝ą░

a797945

ąŚą░ą│ąŠą╗ąŠą▓ąŠą║ čüąŠąŠą▒čēąĄąĮąĖčÅ: Re: stm32+AD9238. High-speed ADC. ąÜą░ąĮą░ą╗čŗ ąÉ ąĖ ąæ. ąØą░čüčéčĆąŠą╣ą║ą░ DM

ąöąŠą▒ą░ą▓ą╗ąĄąĮąŠ: ą¦čé ą░ą▓ą│ 03, 2023 21:01:15

ą£čāčćąĖč鹥ą╗čī ą╝ąĖą║čĆąŠčüčģąĄą╝

ąÜą░čĆą╝ą░: 4

ąĀąĄą╣čéąĖąĮą│ čüąŠąŠą▒čēąĄąĮąĖą╣: 80

ąŚą░čĆąĄą│ąĖčüčéčĆąĖčĆąŠą▓ą░ąĮ: ąÆčü ąĮąŠčÅ 01, 2015 09:15:16ąĪąŠąŠą▒čēąĄąĮąĖą╣: 445ą×čéą║čāą┤ą░: 69.ąĀąČąĄą▓

ąĀąĄą╣čéąĖąĮą│ čüąŠąŠą▒čēąĄąĮąĖčÅ: 0

čā ąÆą░čü ąĮą░ ą║ą░čĆčéąĖąĮą║ąĄ ąĄčüčéčī ą┐ą░čĆą░ą╝ąĄčéčĆ tpd (ąĘą░ą┤ąĄčƹȹ║ą░ ąŠčé čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĄą│ąŠ čäčĆąŠąĮčéą░ ąĮą░ čāčüčéą░ąĮąŠą▓ą║čā ą┤ą░ąĮąĮčŗčģ ąĮą░ čłąĖąĮąĄ - č鹊ą╗čīą║ąŠ ą┐ąŠčüą╗ąĄ ąĮąĄąĄ ą┤ą░ąĮąĮčŗąĄ ą┤ąŠčüč鹊ą▓ąĄčĆąĮčŗ) ą┐ąŠ č鹥ą║čüčéčā čā ąÆą░čü ąŠ ąĮąĄą╝ ąĮąĖ čüą╗ąŠą▓ą░.

ąÆąĄčĆąĮčāčéčīčüčÅ ąĮą░ą▓ąĄčĆčģ

ąĀąĄą║ą╗ą░ą╝ą░

>TEHb<

ąŚą░ą│ąŠą╗ąŠą▓ąŠą║ čüąŠąŠą▒čēąĄąĮąĖčÅ: Re: stm32+AD9238. High-speed ADC. ąÜą░ąĮą░ą╗čŗ ąÉ ąĖ ąæ. ąØą░čüčéčĆąŠą╣ą║ą░ DM

ąöąŠą▒ą░ą▓ą╗ąĄąĮąŠ: ą¦čé ą░ą▓ą│ 03, 2023 21:50:27

ąöčĆčāą│ ąÜąŠčéą░

ąÜą░čĆą╝ą░: 13

ąĀąĄą╣čéąĖąĮą│ čüąŠąŠą▒čēąĄąĮąĖą╣: 359

ąŚą░čĆąĄą│ąĖčüčéčĆąĖčĆąŠą▓ą░ąĮ: ąĪčĆ ąĮąŠčÅ 11, 2009 17:19:30ąĪąŠąŠą▒čēąĄąĮąĖą╣: 4323ą×čéą║čāą┤ą░: ąÆąŠčĆąŠąĮąĄąČ

ąĀąĄą╣čéąĖąĮą│ čüąŠąŠą▒čēąĄąĮąĖčÅ: 0

dimaib ą┐ąĖčüą░ą╗(ą░):

ą┐čĆąĄčĆčŗą▓ą░ąĮąĖą╣ ąĮą░ čŹč鹊čé čüą╗čāčćą░ą╣ ąĮąĄčé.

dimaib ą┐ąĖčüą░ą╗(ą░):

ąĖčüą┐ąŠą╗čīąĘčāąĄčéčüčÅ DCMI ąĖ DMA

ą¤čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ąĖ ąĮąĄ ąĮčāąČąĮčŗ. ąÉ ąĄčüą╗ąĖ čāąČ ą╝ąŠąČąĮąŠ ą┐ąŠąĘą▓ąŠą╗ąĖčéčī čüąĄą▒ąĄ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ, č鹊 ą▓čüčÅą║ąĖąĄ ą┐čĆąŠčćąĖąĄ ąĖąĮč鹥čĆč乥ą╣čüčŗ ąĖ ąĮąĄ čéčĆąĄą▒čāčÄčéčüčÅ.

dimaib ą┐ąĖčüą░ą╗(ą░):

ą¦ą░čüč鹊čéą░ čéą░ą║čéąĖčĆąŠą▓ą░ąĮąĖčÅ ą┤ąŠą╗ąČąĮą░ ą▒čŗčéčī ąĮąĄ ą╝ąĄąĮąĄąĄ 4ą£ąōčå.

dimaib ą┐ąĖčüą░ą╗(ą░):

ą┤ą░ąĮąĮčŗąĄ čéčĆąĄą▒čāąĄčéčüčÅ čüčćąĖčéčŗą▓ą░čéčī čü čćą░čüč鹊č鹊ą╣ ąĮąĄ ą╝ąĄąĮąĄąĄ 4ą£ąōčå

ąŁč鹊 čĆą░ąĘąĮčŗąĄ ą▓ąĄčēąĖ. ą¦č鹊 čéčĆąĄą▒čāąĄčéčüčÅ ą▓čüčæ-čéą░ą║ąĖ? ąÉ ąĄčüą╗ąĖ 16-ą▒ąĖčéąĮčŗąĄ ąÉą”ą¤ ąĘą░ą┐čāčüčéąĖčéčī ą▓ čĆą░ąĘčĆąĄčłąĄąĮąĖąĖ 12 ą▒ąĖčé, č鹊 ą▓čüčæ čĆą░ą▓ąĮąŠ ą╝ą░ą╗ąŠ čüą║ąŠčĆąŠčüčéąĖ?

ąÆąĄčĆąĮčāčéčīčüčÅ ąĮą░ą▓ąĄčĆčģ

ąĀąĄą║ą╗ą░ą╝ą░

dimaib

ąŚą░ą│ąŠą╗ąŠą▓ąŠą║ čüąŠąŠą▒čēąĄąĮąĖčÅ: Re: stm32+AD9238. High-speed ADC. ąÜą░ąĮą░ą╗čŗ ąÉ ąĖ ąæ. ąØą░čüčéčĆąŠą╣ą║ą░ DM

ąöąŠą▒ą░ą▓ą╗ąĄąĮąŠ: ą¤čé ą░ą▓ą│ 04, 2023 00:48:55

ą¤ąĄčĆą▓čŗą╣ čĆą░ąĘ čüą║ą░ąĘą░ą╗ ą£čÅčā!

ąŚą░čĆąĄą│ąĖčüčéčĆąĖčĆąŠą▓ą░ąĮ: ąĪą▒ ą░ą┐čĆ 02, 2011 04:05:00ąĪąŠąŠą▒čēąĄąĮąĖą╣: 33

ąĀąĄą╣čéąĖąĮą│ čüąŠąŠą▒čēąĄąĮąĖčÅ: 0

ą”ąĖčéą░čéą░:

ą¤čĆąĄčĆčŗą▓ą░ąĮąĖčÅ ąĖ ąĮąĄ ąĮčāąČąĮčŗ. ąÉ ąĄčüą╗ąĖ čāąČ ą╝ąŠąČąĮąŠ ą┐ąŠąĘą▓ąŠą╗ąĖčéčī čüąĄą▒ąĄ ą┐čĆąĄčĆčŗą▓ą░ąĮąĖčÅ, č鹊 ą▓čüčÅą║ąĖąĄ ą┐čĆąŠčćąĖąĄ ąĖąĮč鹥čĆč乥ą╣čüčŗ ąĖ ąĮąĄ čéčĆąĄą▒čāčÄčéčüčÅ.

čÅ ą│ąŠą▓ąŠčĆąĖą╗ ą┐čĆąŠ ą┐čĆąĄčĆą▓čŗą▓ą░ąĮąĖčÅ č鹊ą╗čīą║ąŠ ą┤ą╗čÅ ąŠčéą╗ą░ą┤ą║ąĖ, čćč鹊 ą▒čŗ ąĘąĮą░čéčī, ą│ą┤ąĄ ąĖ ą║ąŠą│ą┤ą░ čćč鹊 ą┐čĆąŠąĖčüčģąŠą┤ąĖčé.

ą”ąĖčéą░čéą░:

ąŁč鹊 čĆą░ąĘąĮčŗąĄ ą▓ąĄčēąĖ. ą¦č鹊 čéčĆąĄą▒čāąĄčéčüčÅ ą▓čüčæ-čéą░ą║ąĖ? ąÉ ąĄčüą╗ąĖ 16-ą▒ąĖčéąĮčŗąĄ ąÉą”ą¤ ąĘą░ą┐čāčüčéąĖčéčī ą▓ čĆą░ąĘčĆąĄčłąĄąĮąĖąĖ 12 ą▒ąĖčé, č鹊 ą▓čüčæ čĆą░ą▓ąĮąŠ ą╝ą░ą╗ąŠ čüą║ąŠčĆąŠčüčéąĖ?

ąŚą░ą┤ą░čćą░ čüąĖąĮčģčĆąŠąĮąĖąĘąĖčĆąŠą▓ą░čéčī čĆą░ą▒ąŠčéčā ą£ąÜ ąĖ ą▓ąĮąĄčłąĮąĄą│ąŠ ą▓ą┤čāčģą║ą░ąĮą░ą╗čīąĮąŠą│ąŠ ąÉą”ą¤.

ą”ąĖčéą░čéą░:

čā ąÆą░čü ąĮą░ ą║ą░čĆčéąĖąĮą║ąĄ ąĄčüčéčī ą┐ą░čĆą░ą╝ąĄčéčĆ tpd (ąĘą░ą┤ąĄčƹȹ║ą░ ąŠčé čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĄą│ąŠ čäčĆąŠąĮčéą░ ąĮą░ čāčüčéą░ąĮąŠą▓ą║čā ą┤ą░ąĮąĮčŗčģ ąĮą░ čłąĖąĮąĄ - č鹊ą╗čīą║ąŠ ą┐ąŠčüą╗ąĄ ąĮąĄąĄ ą┤ą░ąĮąĮčŗąĄ ą┤ąŠčüč鹊ą▓ąĄčĆąĮčŗ) ą┐ąŠ č鹥ą║čüčéčā čā ąÆą░čü ąŠ ąĮąĄą╝ ąĮąĖ čüą╗ąŠą▓ą░.

ąöą░ čÅ ą┐ąŠąĮčÅą╗, čćč鹊 čéčĆąĄą▒čāąĄčéčüčÅ čüą╝ąĄčüčéąĖčéčī čéą░ą║č鹊ą▓čāčÄ čćą░čüč鹊čéčā ąÉą”ą¤ ą┐ąŠ čäą░ąĘąĄ. ąĪąĄą╣čćą░čü ą▒čīčÄčüčī ąĮą░ą┤ čŹčéąĖą╝. ąÆčüąĄ čćą░čüč鹊čéčŗ ą┐ąŠą║ą░ ą┐ą╗ą░ą▓čāčé.

ąØą░čüčéčĆąŠąĖą╗ ą┤ąŠą┐ąŠą╗ąĮąĖč鹥ą╗čīąĮčŗą╣ čéą░ą╣ą╝ąĄčĆ ą▓ TOGGLE čĆąĄąČąĖą╝ąĄ, ąĮą░ čćą░čüč鹊čéčā ą▓ 2 čĆą░ąĘą░ ą╝ąĄąĮčīčłąĄ. ąØąŠ ą┐ąŠą║ą░ ąĮąĄ ą┐ąŠą╗čāčćą░ąĄčéčüčÅ čüąĖąĮčģčĆąŠąĮąĖąĘąĖčĆąŠą▓ą░čéčī.

ąöąŠą▒ą░ą▓ą╗ąĄąĮąŠ after 2 hours 50 minutes 24 seconds: Re: stm32+AD9238. High-speed ADC. ąÜą░ąĮą░ą╗čŗ ąÉ ąĖ ąæ. ąØą░čüčéčĆąŠą╣ą║ą░ DMA ą¤čŗčéą░ą╗čüčÅ čüą┤ąĄą╗ą░čéčī čüą╗ąĄą┤čāčÄčēąĄąĄ:

ąÆčŗą║ąĖąĮčāą╗ ą┤ąĄą╗ąĖč鹥ą╗čī čćą░čüč鹊čéčŗ ąĮą░ JK-čéčĆąĖą│ą│ąĄčĆąĄ. ąÆą╝ąĄčüč鹊 ąĮąĄą│ąŠ ąĮą░čüčéčĆąŠąĖą╗ ąŠčéą┤ąĄą╗čīąĮčŗą╣ čéą░ą╣ą╝ąĄčĆ ąĖ ą┤ą╗čÅ ąĮą░čćą░ą╗ą░ čüąĖąĮčģčĆąŠąĮąĖąĘąĖčĆąŠą▓ą░ą╗ ąĄą│ąŠ čü čéą░ą║čéąĖčĆąŠą▓ą░ąĮąĖąĄą╝ DCMI, ą┐ąŠč鹊ą╝ čĆą░ąĘą┤ąĄą╗ąĖą╗ čŹčéčā čćą░čüč鹊čéčā ąĮą░ 2.

ąöąŠą▒ą░ą▓ąĖą╗ čüą╝ąĄčēąĄąĮąĖąĄ ąŠą┤ąĮąŠą│ąŠ čüąĖą│ąĮą░ą╗ą░ ąŠčéąĮąŠčüąĖč鹥ą╗čīąĮąŠ ą┤čĆčāą│ąŠą│ąŠ. ąś ą┐čŗčéą░ą╗čüčÅ ą┐ąŠą┤ąŠą▒čĆą░čéčī čŹč鹊 čüą╝ąĄčēąĄąĮąĖąĄ.

ąóą░ą║ ąČąĄ ą┐čŗčéą░ą╗čüčÅ ąĖąĮą▓ąĄčĆčéąĖčĆąŠą▓ą░čéčī ąŠą┤ąĮąŠ čéą░ą║čéąĖčĆąŠą▓ą░ąĮąĖąĄ ąŠčéąĮąŠčüąĖč鹥ą╗čīąĮąŠ ą┤čĆčāą│ąŠą│ąŠ.

ąĀąĄąĘčāą╗čīčéą░čéčŗ ąŠčüčéą░čÄčéčüčÅ ąĮąĄąĖąĘą╝ąĄąĮąĮčŗą╝ąĖ, ą╝ą░čüčüąĖą▓ ąĘą░ą┐ąŠą╗ąĮčÅąĄčéčüčÅ čĆą░ąĮą┤ąŠą╝ąĮąŠ. ąóąŠ ą║ą░ąĮą░ą╗ąŠą╝ ąÉ, č鹊 ą║ą░ąĮą░ą╗ąŠą╝ ąæ..

ąØą░ čüą║čĆąĖąĮčłąŠč鹥 ą┐ąŠą║ą░ąĘą░ą╗, čćč鹊 ą┤ą░ąČąĄ ąĮą░ ą╝ą░ą╗ąĄąĮčīą║ąĖčģ čüą║ąŠčĆąŠčüčéčģ, čŹč鹊 ąĮąĄ čĆą░ą▒ąŠčéą░ąĄčé. ąóą░ą║ ąČąĄ ą▓ąĖą┤ąĮąŠ, čćč鹊 čćą░čüč鹊čéčŗ čéą░ą║čéąĖčĆąŠą▓ą░ąĮąĖčÅ ąŠčéą╗ąĖčćą░čÄčéčüčÅ ą▓ ą┤ą▓ą░ čĆą░ąĘą░ ąĖ ąĄčüčéčī čüą╝ąĄčēąĄąĮąĖąĄ.

ąŻ ą║ąŠą│ąŠ č鹊 ąĄčüčéčī ą║ą░ą║ąĖąĄ č鹊 ąĖą┤ąĄąĖ?

ąĪą┐ą░čüąĖą▒ąŠ, ą▓ą░ą╝!

ąÆąĄčĆąĮčāčéčīčüčÅ ąĮą░ą▓ąĄčĆčģ

jcxz

ąŚą░ą│ąŠą╗ąŠą▓ąŠą║ čüąŠąŠą▒čēąĄąĮąĖčÅ: Re: stm32+AD9238. High-speed ADC. ąÜą░ąĮą░ą╗čŗ ąÉ ąĖ ąæ. ąØą░čüčéčĆąŠą╣ą║ą░ DM

ąöąŠą▒ą░ą▓ą╗ąĄąĮąŠ: ą¤čé ą░ą▓ą│ 04, 2023 02:10:34

ąĪą▓ąĄčĆą╗ąĖčé č鹥ą║čüč鹊ą╗ąĖčé ą║ąŠą│čéčÅą╝ąĖ

ąÜą░čĆą╝ą░: -10

ąĀąĄą╣čéąĖąĮą│ čüąŠąŠą▒čēąĄąĮąĖą╣: 100

ąŚą░čĆąĄą│ąĖčüčéčĆąĖčĆąŠą▓ą░ąĮ: ąÆčé ą░ą▓ą│ 15, 2017 10:51:13ąĪąŠąŠą▒čēąĄąĮąĖą╣: 1156

ąĀąĄą╣čéąĖąĮą│ čüąŠąŠą▒čēąĄąĮąĖčÅ: 0

ąŻ ą║ąŠą│ąŠ č鹊 ąĄčüčéčī ą║ą░ą║ąĖąĄ č鹊 ąĖą┤ąĄąĖ?

ąŚą░č湥ą╝ ą▓čüąĄ čŹčéąĖ čüą╗ąŠąČąĮąŠčüčéąĖ čü ą┐ą░čĆą░ą╗ą╗ąĄą╗čīąĮčŗą╝ąĖ čłąĖąĮą░ą╝ąĖ ąĖ čé.ą┐.? ą¤ąŠč湥ą╝čā ąĮąĄ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčī ąÉą”ą¤ ą▓čüčéčĆąŠąĄąĮąĮčŗą╣ ą▓ ą£ąÜ?

ąÆąĄčĆąĮčāčéčīčüčÅ ąĮą░ą▓ąĄčĆčģ

dimaib

ąŚą░ą│ąŠą╗ąŠą▓ąŠą║ čüąŠąŠą▒čēąĄąĮąĖčÅ: Re: stm32+AD9238. High-speed ADC. ąÜą░ąĮą░ą╗čŗ ąÉ ąĖ ąæ. ąØą░čüčéčĆąŠą╣ą║ą░ DM

ąöąŠą▒ą░ą▓ą╗ąĄąĮąŠ: ą¤čé ą░ą▓ą│ 04, 2023 02:28:58

ą¤ąĄčĆą▓čŗą╣ čĆą░ąĘ čüą║ą░ąĘą░ą╗ ą£čÅčā!

ąŚą░čĆąĄą│ąĖčüčéčĆąĖčĆąŠą▓ą░ąĮ: ąĪą▒ ą░ą┐čĆ 02, 2011 04:05:00ąĪąŠąŠą▒čēąĄąĮąĖą╣: 33

ąĀąĄą╣čéąĖąĮą│ čüąŠąŠą▒čēąĄąĮąĖčÅ: 0

ą”ąĖčéą░čéą░:

ąŚą░č湥ą╝ ą▓čüąĄ čŹčéąĖ čüą╗ąŠąČąĮąŠčüčéąĖ čü ą┐ą░čĆą░ą╗ą╗ąĄą╗čīąĮčŗą╝ąĖ čłąĖąĮą░ą╝ąĖ ąĖ čé.ą┐.? ą¤ąŠč湥ą╝čā ąĮąĄ ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčī ąÉą”ą¤ ą▓čüčéčĆąŠąĄąĮąĮčŗą╣ ą▓ ą£ąÜ?

ą┐ąŠč鹊ą╝čā čćč鹊 ą▓ ą▒čāą┤čāčēąĄą╝ ą┐ą╗ą░ąĮąĖčĆčāąĄčéčüčÅ čāą▓ąĄą╗ąĖč湥ąĮąĖąĄ čćą░čüč鹊čéčŗ čüąĄą╝ą┐ą╗ąĖčĆąŠą▓ą░ąĮąĖčÅ, čü ą║ąŠč鹊čĆąŠą╣ ąĮąĄ čüą┐čĆą░ą▓ą╗čÅąĄčéčüčÅ ą▓ąĮčāčéčĆąĄąĮąĮąĖą╣ ąÉą”ą¤

ąÆąĄčĆąĮčāčéčīčüčÅ ąĮą░ą▓ąĄčĆčģ

jcxz

ąŚą░ą│ąŠą╗ąŠą▓ąŠą║ čüąŠąŠą▒čēąĄąĮąĖčÅ: Re: stm32+AD9238. High-speed ADC. ąÜą░ąĮą░ą╗čŗ ąÉ ąĖ ąæ. ąØą░čüčéčĆąŠą╣ą║ą░ DM

ąöąŠą▒ą░ą▓ą╗ąĄąĮąŠ: ą¤čé ą░ą▓ą│ 04, 2023 02:34:53

ąĪą▓ąĄčĆą╗ąĖčé č鹥ą║čüč鹊ą╗ąĖčé ą║ąŠą│čéčÅą╝ąĖ

ąÜą░čĆą╝ą░: -10

ąĀąĄą╣čéąĖąĮą│ čüąŠąŠą▒čēąĄąĮąĖą╣: 100

ąŚą░čĆąĄą│ąĖčüčéčĆąĖčĆąŠą▓ą░ąĮ: ąÆčé ą░ą▓ą│ 15, 2017 10:51:13ąĪąŠąŠą▒čēąĄąĮąĖą╣: 1156

ąĀąĄą╣čéąĖąĮą│ čüąŠąŠą▒čēąĄąĮąĖčÅ: 0

ą┐ąŠč鹊ą╝čā čćč鹊 ą▓ ą▒čāą┤čāčēąĄą╝ ą┐ą╗ą░ąĮąĖčĆčāąĄčéčüčÅ čāą▓ąĄą╗ąĖč湥ąĮąĖąĄ čćą░čüč鹊čéčŗ čüąĄą╝ą┐ą╗ąĖčĆąŠą▓ą░ąĮąĖčÅ, čü ą║ąŠč鹊čĆąŠą╣ ąĮąĄ čüą┐čĆą░ą▓ą╗čÅąĄčéčüčÅ ą▓ąĮčāčéčĆąĄąĮąĮąĖą╣ ąÉą”ą¤

ąóą░ą║ ą▓čŗą▒ąĄčĆąĖč鹥 čéą░ą║ąŠą╣, ą║ąŠč鹊čĆčŗą╣ čüą┐čĆą░ą▓ąĖčéčüčÅ. ąĢčüą╗ąĖ čāąČ ąĮčāąČąĮą░ ą▓čŗčüąŠą║ą░čÅ čćą░čüč鹊čéą░ čü菹╝ą┐ą╗ąĖčĆąŠą▓ą░ąĮąĖčÅ, č鹊 ąŠą┤ąĮąŠąĘąĮą░čćąĮąŠ ąĮąĖą║ą░ą║ąĖą╝ąĖ čāčģąĖčēčĆąĄąĮąĖčÅą╝ąĖ ąĮąĄ čüą╝ąŠąČąĄč鹥 čćąĖčéą░čéčī ą▓ čĆąĄą░ą╗čīąĮąŠą╝ ą▓čĆąĄą╝ąĄąĮąĖ ąĖąĘ ąĮąĄą│ąŠ čü čéą░ą║ąŠą╣ čüą║ąŠčĆąŠčüčéčīčÄ, čü ą║ą░ą║ąŠą╣ ą▓ąĮčāčéčĆąĄąĮąĮąĖą╣ ąÉą”ą¤ ą┐ąŠąĘą▓ąŠą╗čÅąĄčé. ą×ąĮ 100 ąŠčćą║ąŠą▓ ą▓ą┐ąĄčĆčæą┤ ą┤ą░čüčé ą▓ąĮąĄčłąĮąĄą╝čā. ąóą░ą║ ą║ą░ą║ čéą░ą╝ ąĖ čłąĖąĮą░ 32-ą▒ąĖčéąĮą░čÅ (ą░ ąĮąĄ ą┤ąŠčģą╗čŗąĄ 12 ą▒ąĖčé) ąĖ čüąŠą┐čĆčÅąČąĄąĮąĖąĄ čü DMA ąĮąŠčĆą╝ą░ą╗čīąĮąŠ čüą┤ąĄą╗ą░ąĮąŠ, ą▒ąĄąĘ ą║ąŠčüčéčŗą╗ąĄą╣ čüąŠ čüą┤ą▓ąĖą│ą░ą╝ąĖ čäą░ąĘčŗ ą║ą░ą║ čā ą▓ą░čü.

ąÆąĄčĆąĮčāčéčīčüčÅ ąĮą░ą▓ąĄčĆčģ

dimaib

ąŚą░ą│ąŠą╗ąŠą▓ąŠą║ čüąŠąŠą▒čēąĄąĮąĖčÅ: Re: stm32+AD9238. High-speed ADC. ąÜą░ąĮą░ą╗čŗ ąÉ ąĖ ąæ. ąØą░čüčéčĆąŠą╣ą║ą░ DM

ąöąŠą▒ą░ą▓ą╗ąĄąĮąŠ: ą¤čé ą░ą▓ą│ 04, 2023 09:16:43

ą¤ąĄčĆą▓čŗą╣ čĆą░ąĘ čüą║ą░ąĘą░ą╗ ą£čÅčā!

ąŚą░čĆąĄą│ąĖčüčéčĆąĖčĆąŠą▓ą░ąĮ: ąĪą▒ ą░ą┐čĆ 02, 2011 04:05:00ąĪąŠąŠą▒čēąĄąĮąĖą╣: 33

ąĀąĄą╣čéąĖąĮą│ čüąŠąŠą▒čēąĄąĮąĖčÅ: 0

ąÆąŠąĘą╝ąŠąČąĮąŠ, ą▓čŗ ą┐čĆą░ą▓čŗ! ąĢčüą╗ąĖ ąĮą░ čÅ čüą╝ąŠą│čā ą┐ąŠą┤ąŠą▒čĆą░čéčī ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆ pin-to-pin, ąĮąŠ ą┐ąŠą║ą░ čÅ ąĮąĄ čüą╝ąŠą│ ąĮą░ą╣čéąĖ ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆ čģąŠčéčÅ ą▒čŗ ą▓ čĆą░ą╣ąŠąĮąĄ čćą░čüč鹊čéčŗ čüąĄą╝ą╗ąĖčĆąŠą▓ą░ąĮąĖčÅ 20MSPS.

ąöąŠą▒ą░ą▓ą╗ąĄąĮąŠ after 14 minutes 58 seconds: Re: stm32+AD9238. High-speed ADC. ąÜą░ąĮą░ą╗čŗ ąÉ ąĖ ąæ. ąØą░čüčéčĆąŠą╣ą║ą░ DMA ąØąŠ ą║ą░ą║ ąŠą▒čŗčćąĮąŠ ą▒čŗą▓ą░ąĄčé, ąĖ ą┤čāą╝ą░čÄ čéą░ą║ąŠąĄ ą▒čŗą╗ąŠ čā ą▓čüąĄčģ, ą┐ą░čĆčéąĖčÅ ą│ąŠč鹊ą▓čŗčģ ąĖ čüą┐ą░čÅąĮąĮčŗčģ ą┐ą╗ą░čé ą╗ąĄąČąĖčé ą┐ąĄčĆąĄą┤ąŠą╝ąĮąŠą╣ ąĮą░ čüč鹊ą╗ąĄ ąĖ čā ą╝ąĄąĮčÅ ąĄčüčéčī ąĘą░ą┤ą░čćą░ ąŠčéą╗ą░ą┤ąĖčéčī ąĖ ąĘą░ą┐čāčüčéąĖčéčī čŹč鹊 čćčāą┤ąŠ, ąĖą╝ąĄąĮąĮąŠ ą┐ąŠčŹč鹊ą╝čā čÅ ąĘą░ą┤ą░ą╗ čŹč鹊čé ą▓ąŠą┐čĆąŠčü ąĮą░ č乊čĆčāą╝ąĄ.

ą» ą▓ąĖą┤ąĄą╗ ąĮąĄą║ąŠč鹊čĆčŗąĄ čüčéą░čéčīąĖ ąĮą░ č鹥ą╝čā čüąŠą▓ą╝ąĄčēąĄąĮąĖčÅ ą┐ą░čĆą░ą╗ą╗ąĄą╗čīąĮčŗčģ ą▓ą░čüąŠą║ąŠčüą║ąŠčĆąŠčüčéąĮčŗčģ ą╝ąĖą║čĆąŠčüčģąĄą╝ ąÉą”ą¤ ąĖ ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆąŠą▓ ąĪąóą£ čü ą┐ąŠą╝ąŠčēčīčÄ DCMI.. ąÆąŠčé ą║ ą┐čĆąĖą╝ąĄčĆčā:

https://habr.com/ru/articles/482506/ viewtopic.php?p=3677112 https://github.com/cychenbuaa/Driving-A ... r_pto=wapp ąØąŠ ąĘą░ą┤ą░čćą░ ą╝čāą╗čīčéąĖą┐ą╗ąĄą║čüąĖčĆąŠą▓ą░ąĮąĖčÅ ą▓čŗčģąŠą┤ąŠą▓ ąĮą░ ąŠą┤ąĮčā čłąĖąĮčā ą┐ąĄčĆąĄą┤ ąĮąĖą╝ąĖ ąĮąĄ čüč鹊čÅą╗ą░, ąĖ ąĮąĄ ą┐čĆąĄą┤čüčéą░ą▓ą╗čÅčÄ ą║ą░ą║ čŹč鹊 ąŠčéą╗ą░ą┤ąĖčéčī.

ą» ąĮą░ą┤ąĄčÅą╗čüčÅ ą╝ąĮąĄ čéčāčé ą┐ąŠą╝ąŠą│čāčé čü čŹčéąĖą╝

ąÆąĄčĆąĮčāčéčīčüčÅ ąĮą░ą▓ąĄčĆčģ

>TEHb<

ąŚą░ą│ąŠą╗ąŠą▓ąŠą║ čüąŠąŠą▒čēąĄąĮąĖčÅ: Re: stm32+AD9238. High-speed ADC. ąÜą░ąĮą░ą╗čŗ ąÉ ąĖ ąæ. ąØą░čüčéčĆąŠą╣ą║ą░ DM

ąöąŠą▒ą░ą▓ą╗ąĄąĮąŠ: ą¤čé ą░ą▓ą│ 04, 2023 09:26:33

ąöčĆčāą│ ąÜąŠčéą░

ąÜą░čĆą╝ą░: 13

ąĀąĄą╣čéąĖąĮą│ čüąŠąŠą▒čēąĄąĮąĖą╣: 359

ąŚą░čĆąĄą│ąĖčüčéčĆąĖčĆąŠą▓ą░ąĮ: ąĪčĆ ąĮąŠčÅ 11, 2009 17:19:30ąĪąŠąŠą▒čēąĄąĮąĖą╣: 4323ą×čéą║čāą┤ą░: ąÆąŠčĆąŠąĮąĄąČ

ąĀąĄą╣čéąĖąĮą│ čüąŠąŠą▒čēąĄąĮąĖčÅ: 0

ąóąŠą│ą┤ą░ ą┤ą░ą▓ą░ą╣č鹥 ą░ą║čéčāą░ą╗čīąĮčāčÄ čüčģąĄą╝čā. ą¤ąŠą┤ąŠąĘčĆąĄą▓ą░čÄ, čćč鹊 ąĘą░čéčŗą║ ą║ą░ą║ąŠą╣-č鹊 ą▓ąŠą▓čüąĄ ąĮąĄ ą▓ąĄą╗ąĖą║ąĖą╣.

ąÆąĄčĆąĮčāčéčīčüčÅ ąĮą░ą▓ąĄčĆčģ

jcxz

ąŚą░ą│ąŠą╗ąŠą▓ąŠą║ čüąŠąŠą▒čēąĄąĮąĖčÅ: Re: stm32+AD9238. High-speed ADC. ąÜą░ąĮą░ą╗čŗ ąÉ ąĖ ąæ. ąØą░čüčéčĆąŠą╣ą║ą░ DM

ąöąŠą▒ą░ą▓ą╗ąĄąĮąŠ: ą¤čé ą░ą▓ą│ 04, 2023 10:10:00

ąĪą▓ąĄčĆą╗ąĖčé č鹥ą║čüč鹊ą╗ąĖčé ą║ąŠą│čéčÅą╝ąĖ

ąÜą░čĆą╝ą░: -10

ąĀąĄą╣čéąĖąĮą│ čüąŠąŠą▒čēąĄąĮąĖą╣: 100

ąŚą░čĆąĄą│ąĖčüčéčĆąĖčĆąŠą▓ą░ąĮ: ąÆčé ą░ą▓ą│ 15, 2017 10:51:13ąĪąŠąŠą▒čēąĄąĮąĖą╣: 1156

ąĀąĄą╣čéąĖąĮą│ čüąŠąŠą▒čēąĄąĮąĖčÅ: 0

ąØąŠ ą║ą░ą║ ąŠą▒čŗčćąĮąŠ ą▒čŗą▓ą░ąĄčé, ąĖ ą┤čāą╝ą░čÄ čéą░ą║ąŠąĄ ą▒čŗą╗ąŠ čā ą▓čüąĄčģ, ą┐ą░čĆčéąĖčÅ ą│ąŠč鹊ą▓čŗčģ ąĖ čüą┐ą░čÅąĮąĮčŗčģ ą┐ą╗ą░čé ą╗ąĄąČąĖčé ą┐ąĄčĆąĄą┤ąŠą╝ąĮąŠą╣ ąĮą░ čüč鹊ą╗ąĄ

ąØąĄčé, čéą░ą║ ą▒čŗą▓ą░ąĄčé č鹊ą╗čīą║ąŠ čā č鹥čģ, ą║č鹊 čüčéą░ą▓ąĖčé č鹥ą╗ąĄą│čā ą▓ą┐ąĄčĆąĄą┤ąĖ ą╗ąŠčłą░ą┤ąĖ. ąŻ č鹥čģ, čā ą║ąŠą│ąŠ ąĄčüčéčī ą│ąŠą╗ąŠą▓ą░ ąĮą░ ą┐ą╗ąĄčćą░čģ, čéą░ą║ąŠą│ąŠ ąĮąĄ ą▒čŗą▓ą░ąĄčé, ą┐ąŠč鹊ą╝čā ą║ą░ą║ čüą┐ąĄčĆą▓ą░ ą┤ąĄą╗ą░ąĄčéčüčÅ ą┐ąŠąĖčüą║ ąĮą░ąĖą▒ąŠą╗ąĄąĄ ąŠą┐čéąĖą╝ą░ą╗čīąĮąŠą│ąŠ čĆąĄčłąĄąĮąĖčÅ ąĘą░ą┤ą░čćąĖ (ąĖ ąĮą░ąĖą▒ąŠą╗ąĄąĄ ąŠą┐čéąĖą╝ą░ą╗čīąĮąŠą│ąŠ ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░), ą┐ąŠč鹊ą╝ - ą╝ą░ą║ąĄčéąĖčĆąŠą▓ą░ąĮąĖąĄ ąĮą░ ąŠčéą╗ą░ą┤ąŠčćąĮčŗčģ ą┐ą╗ą░čéą░čģ. ąÉ ąĖąĘą│ąŠč鹊ą▓ą╗ąĄąĮąĖąĄ čüą▓ąŠąĖčģ ą┐ą╗ą░čé - čŹč鹊 ą║ąŠą│ą┤ą░ čāąČąĄ ą▓čüąĄ čĆąĄčłąĄąĮąĖčÅ ąŠčéčĆą░ą▒ąŠčéą░ąĮčŗ ąĮą░ ą╝ą░ą║ąĄčéą║ą░čģ

ąĖ č鹊čćąĮąŠ čĆą░ą▒ąŠčéą░čÄčé .

ąŻ č鹥čģ ą║č鹊 ą┐ą░čÅąĄčé ą┐ą░čĆčéąĖčÄ ą┐ą╗ą░čé(!)

, ą░ č鹊ą╗čīą║ąŠ ą┐ąŠč鹊ą╝ ąĮą░čćąĖąĮą░ąĄčé ą┤čāą╝ą░čéčī, ą║ą░ą║ ą┐čĆą░ą▓ąĖą╗ąŠ - ąĖą╗ąĖ čŹčéą░ ą┐ą░čĆčéąĖčÅ ąĖą┤čæčé ą▓ ą╝čāčüąŠčĆąĮčāčÄ ą║ąŠčƹʹĖąĮčā; ąĖą╗ąĖ ą┤ąŠą╗ą│ąŠ ąĖ ą╝čāčćąĖč鹥ą╗čīąĮąŠ ą┐ąŠč鹊ą╝ ą║ąŠčüčéčŗą╗ąĖčéčüčÅ, čćč鹊ą▒čŗ čģąŠčéčī ą║ą░ą║-č鹊 ą┤ąŠčéčÅąĮčāčéčī ą┤ąŠ čéčĆąĄą▒ąŠą▓ą░ąĮąĖą╣ (č湥ą│ąŠ ąŠą▒čŗčćąĮąŠ ąĮąĄ ą┐ąŠą╗čāčćą░ąĄčéčüčÅ, ą░ ąŠčüčéą░čæčéčüčÅ "čćč鹊 ą┐ąŠą╗čāčćąĖą╗ąŠčüčī").

ąĪčéčĆą░ąĮąĮąŠ, čćč鹊 ą▓ą░ą╝ ą┤ą░ąČąĄ ąĮąĄ ą┐čĆąĖčłą╗ąŠ ą▓ ą│ąŠą╗ąŠą▓čā ą┐čĆąŠą╝ą░ą║ąĄčéąĖčĆąŠą▓ą░čéčī čüą▓ąŠčæ čĆąĄčłąĄąĮąĖąĄ. ąŻąČ ąĮąĄ ą│ąŠą▓ąŠčĆčÅ ąŠ č鹊ą╝ čćč鹊ą▒čŗ ą┐čĆąŠčüč鹊 ą┐ąŠąĖčüą║ą░čéčī ą▒ąŠą╗ąĄąĄ ą┐ąŠą┤čģąŠą┤čÅčēąĖą╣ ą£ąÜ, ą░ ąĮąĄ ą▒čĆą░čéčī ą┐ąĄčĆą▓čŗą╣ ą┐ąŠą┐ą░ą▓čłąĖą╣čüčÅ ą┐ąŠą┤ čĆčāą║čā.

ą» ąĮą░ą┤ąĄčÅą╗čüčÅ ą╝ąĮąĄ čéčāčé ą┐ąŠą╝ąŠą│čāčé čü čŹčéąĖą╝

ą¤ąŠą║ą░ ą┐ąŠč鹥čĆčÅąĮčŗ č鹊ą╗čīą║ąŠ ą┤ąĄąĮčīą│ąĖ ąĮą░ ąĖąĘą│ąŠč鹊ą▓ą╗ąĄąĮąĖąĄ ą┐ą╗ą░čé, ąĮąŠ ąĄčēčæ ąĮąĄ ą┐ąŠč鹥čĆčÅąĮą░ ą║čāčćą░ ą▓čĆąĄą╝ąĄąĮąĖ, ą┐ąŠą╣čéąĖ ą║ ąĮą░čćą░ą╗čīčüčéą▓čā, ą┐ąŠą▓ąĖąĮąĖčéčīčüčÅ ąĖ čüą▓ąĄčĆąĮčāčéčī ąĮą░ ą┐čĆą░ą▓ąĖą╗čīąĮčŗą╣ ą┐čāčéčī. ąÆąŠčé ą┐čĆą░ą▓ąĖą╗čīąĮąŠąĄ čĆąĄčłąĄąĮąĖąĄ.

PS: ąĢčüą╗ąĖ čāąČ ąĮčāąČąĮą░ ą▓čŗčüąŠą║ą░čÅ čćą░čüč鹊čéą░ čü菹╝ą┐ą╗ąĖčĆąŠą▓ą░ąĮąĖčÅ, č鹊 ą┐ąŠč湥ą╝čā ąĮąĄ ą▓čŗą▒čĆą░ąĮ LPC4370? ąÜąŠč鹊čĆčŗą╣ ą║ č鹊ą╝čā ąČąĄ ąĖ ą║čĆą░čéąĮąŠ ą┤ąĄčłąĄą▓ą╗ąĄ ą▓ą░čłąĄą│ąŠ ą▓čŗą▒ąŠčĆą░? ąś ąĘą░ą┐čāčüą║ą░ąĄčéčüčÅ čü ą┐ąŠą╗ą┐ąĖąĮą║ą░. ąś čüčģąĄą╝ą░ ą┐čĆąŠčüčéą░čÅ. ąś čéą░ą║ąĖčģ čģą░čĆą░ą║č鹥čĆąĖčüčéąĖą║ ą┐ąŠ čüą║ąŠčĆąŠčüčéąĖ čü菹╝ą┐ą╗ąĖčĆąŠą▓ą░ąĮąĖčÅ ą║ą░ą║ čā ąĮąĄą│ąŠ, ąĮą░ ą▓ą░čłąĄą╝ ą┐ą░čĆąŠą▓ąŠąĘąĄ ą┤ą░ąČąĄ ą▒ą╗ąĖąĘą║ąŠ ąĮąĄ ą┤ąŠčüčéąĖčćčī.

ąÆąĄčĆąĮčāčéčīčüčÅ ąĮą░ą▓ąĄčĆčģ

mont-oriol

ąŚą░ą│ąŠą╗ąŠą▓ąŠą║ čüąŠąŠą▒čēąĄąĮąĖčÅ: Re: stm32+AD9238. High-speed ADC. ąÜą░ąĮą░ą╗čŗ ąÉ ąĖ ąæ. ąØą░čüčéčĆąŠą╣ą║ą░ DM

ąöąŠą▒ą░ą▓ą╗ąĄąĮąŠ: ą¤čé ą░ą▓ą│ 04, 2023 12:20:33

ą£čāčćąĖč鹥ą╗čī ą╝ąĖą║čĆąŠčüčģąĄą╝

ąÜą░čĆą╝ą░: 6

ąĀąĄą╣čéąĖąĮą│ čüąŠąŠą▒čēąĄąĮąĖą╣: 112

ąŚą░čĆąĄą│ąĖčüčéčĆąĖčĆąŠą▓ą░ąĮ: ą¤ąĮ ą╝ą░ą╣ 27, 2019 07:18:28ąĪąŠąŠą▒čēąĄąĮąĖą╣: 437ą×čéą║čāą┤ą░: ąÆąÆąź-čüą║

ąĀąĄą╣čéąĖąĮą│ čüąŠąŠą▒čēąĄąĮąĖčÅ: 0

ą¤ąŠą┤čāą╝ą░ą╗, čćč鹊 ąĄčüą╗ąĖ čéą░ą║čéąĖčĆąŠą▓ą░čéčī ąÉą”ą¤ čćą░čüč鹊č鹊ą╣ ą┤ąĄą╗čæąĮąĮąŠą╣ ąĮą░ ą┤ą▓ą░, č鹊 DMA ą▒čāą┤ąĄčé čćąĖčéą░čéčī ą┤ą░ąĮąĮčŗąĄ ąĖ ą▓ ą┐ąĄčĆą▓ąŠą╣ ą┐ąŠą╗ąŠą▓ąĖąĮąĄ ą┐ąĄčĆąĄąŠą┤ą░ ąĖ ą▓ąŠ ą▓č鹊čĆąŠą╣. ąĪąŠą▒čĆą░ą╗ ą┤ąĄą╗ąĖč鹥ą╗čī čćą░čüč鹊čéčŗ ąĮą░ JK-čéčĆąĖą│ąĄčĆąĄ (čćč鹊 ą▒čŗą╗ąŠ ą┐ąŠą┤ čĆčāą║ąŠą╣), ąĖ ą┐ąŠą┤ą░ą╗ ąĮą░ ą▓čģąŠą┤ ą┤ąĄą╗ąĖč鹥ą╗čÅ čćą░čüč鹊čéčŗ, čüąĖą│ąĮą░ą╗ čü ą▓čŗčģąŠą┤ą░ ADC_CLKSRC (čŹč鹊čé čüąĖą│ąĮą░ą╗ čéčĆąĄą▒čāąĄčéčüčÅ ą┤ą╗čÅ ą▓ąĮąĄčłąĮąĄą│ąŠ čéą░ą║čéąĖčĆąŠą▓ą░ąĮąĖčÅ DCMI PIXCLK), ą░ ą║ ą▓čŗčģąŠą┤čā ą┤ąĄą╗ąĖč鹥ą╗čÅ, ą┐ąŠą┤ą║ą╗čÄčćąĖą╗ čéą░ą║čéąĖčĆąŠą▓ą░ąĮąĖąĄ ą║ą░ąĮą░ą╗ąŠą▓ ąÉ, ąæ ąĖ MUX_SELECT.

ąöą░ąĮąĮčŗąĄ ą┐čĆąĖąĮąĖą╝ą░čÄčéčüčÅ ą┐ąŠ čüą┐ą░ą┤čā DCMI_PIXCLK

ąŁč鹊 ąĘąĮą░čćąĖčé, čćč鹊 JK-čéčĆąĖą│ą│ąĄčĆ ą┤ąŠą╗ąČąĄąĮ ą┐ąĄčĆąĄą▓ąŠčĆą░čćąĖą▓ą░čéčīčüčÅ ą┐ąŠ ąĮą░čĆą░čüčéą░ąĮąĖčÄ DCMI_PIXCLK

ą¤čĆąŠą▓ąĄčĆčīč鹥.

ąś ąŠąĮ ą┤ąŠą╗ąČąĄąĮ ą▒čŗčéčī ą╝ą░ą║čüąĖą╝ą░ą╗čīąĮąŠ ą▒čŗčüčéčĆčŗą╝ (ąĖąĮą▓ąĄčĆč鹊čĆčŗ ąĮą░ ą▓čģąŠą┤ąĄ ąĮąĄąČąĄą╗ą░č鹥ą╗čīąĮčŗ ąĖąĘ-ąĘą░ ąĘą░ą┤ąĄčƹȹ║ąĖ).

ąÆąĄčĆąĮčāčéčīčüčÅ ąĮą░ą▓ąĄčĆčģ

dimaib

ąŚą░ą│ąŠą╗ąŠą▓ąŠą║ čüąŠąŠą▒čēąĄąĮąĖčÅ: Re: stm32+AD9238. High-speed ADC. ąÜą░ąĮą░ą╗čŗ ąÉ ąĖ ąæ. ąØą░čüčéčĆąŠą╣ą║ą░ DM

ąöąŠą▒ą░ą▓ą╗ąĄąĮąŠ: ą¤čé ą░ą▓ą│ 04, 2023 19:59:15

ą¤ąĄčĆą▓čŗą╣ čĆą░ąĘ čüą║ą░ąĘą░ą╗ ą£čÅčā!

ąŚą░čĆąĄą│ąĖčüčéčĆąĖčĆąŠą▓ą░ąĮ: ąĪą▒ ą░ą┐čĆ 02, 2011 04:05:00ąĪąŠąŠą▒čēąĄąĮąĖą╣: 33

ąĀąĄą╣čéąĖąĮą│ čüąŠąŠą▒čēąĄąĮąĖčÅ: 0

ą”ąĖčéą░čéą░:

ąóąŠą│ą┤ą░ ą┤ą░ą▓ą░ą╣č鹥 ą░ą║čéčāą░ą╗čīąĮčāčÄ čüčģąĄą╝čā. ą¤ąŠą┤ąŠąĘčĆąĄą▓ą░čÄ, čćč鹊 ąĘą░čéčŗą║ ą║ą░ą║ąŠą╣-č鹊 ą▓ąŠą▓čüąĄ ąĮąĄ ą▓ąĄą╗ąĖą║ąĖą╣.

ąöą░, ą║ąŠąĮąĄčćąĮąŠ! ąĮąĄ ą┐čĆąŠą▒ą╗ąĄą╝ą░! ą» čüąŠą▓ą╝ąĄčüčéąĖą╗ ą▓čüčæ ąĮą░ ąŠą┤ąĮąŠą╝ ą╗ąĖčüč鹥, ą┐ąŠčāą┤ą░ą╗čÅą╗ ą▓čüčæ ą╗ąĖčłąĮąĄąĄ.

ą¤čĆąĖą║čĆąĄą┐ąĖą╗ ąĖ pdf ąĖ ąĖąĘąŠą▒čĆą░ąČąĄąĮąĖąĄ, ąĄčüą╗ąĖ čéčĆąĄą▒čāąĄčéčüčÅ ą╝ąŠą│čā ą▓čŗą╗ąŠąČąĖčéčī ą┐čĆąŠąĄą║čé KiCAD

ąöąŠą▒ą░ą▓ą╗ąĄąĮąŠ after 3 minutes 56 seconds: Re: stm32+AD9238. High-speed ADC. ąÜą░ąĮą░ą╗čŗ ąÉ ąĖ ąæ. ąØą░čüčéčĆąŠą╣ą║ą░ DMA ą”ąĖčéą░čéą░:

ąöą░ąĮąĮčŗąĄ ą┐čĆąĖąĮąĖą╝ą░čÄčéčüčÅ ą┐ąŠ čüą┐ą░ą┤čā DCMI_PIXCLK

mont-oriol , čüą┐ą░čüą▒ąŠ ąĘą░ ąŠčéą▓ąĄčé) ąØąŠ čÅ čāąČąĄ ą┐ąĖčüą░ą╗ ą▓čŗčłąĄ, čćč鹊 ąŠčéą║ą░ąĘą░ą╗čüčÅ ąŠčé ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░ąĮąĖčÅ JK, ąĖ ąĮą░čüčéčĆąŠąĖą╗ ąĖ čüąĖąĮčģčĆąŠąĮąĖąĘąĖčĆąŠą▓ą░ą╗ ąŠčéą┤ąĄą╗čīąĮčŗą╣ čéą░ą╣ą╝ąĄčĆ ą┤ą╗čÅ čéą░ą║čéąĖčĆąŠą▓ą░ąĮąĖčÅ ąÉą”ą¤. ąś ą┤ą░, čÅ ą┐čŗčéą░ą╗čüčÅ ą┤ąĄą╗ą░čéčī čéą░ą║čéąĖčĆąŠą▓ą░ąĮąĖąĄ ą┐čĆčÅą╝čŗą╝ ąĖ ąĖąĮą▓ąĄčĆčéąĮčŗą╝

ąöąŠą▒ą░ą▓ą╗ąĄąĮąŠ after 16 minutes 54 seconds: Re: stm32+AD9238. High-speed ADC. ąÜą░ąĮą░ą╗čŗ ąÉ ąĖ ąæ. ąØą░čüčéčĆąŠą╣ą║ą░ DMA jcxz ą» čåąĄąĮčÄ ą▓ą░čł ąŠą┐čŗčé ąĖ č鹊čćą║čā ąĘčĆąĄąĮąĖčÅ. ą» čüąŠą│ą╗ą░čüąĄąĮ, čćč鹊 ą▓ą░ąČąĮąŠ ą╝ą░ą║ąĄčéąĖčĆąŠą▓ą░čéčī ąĖ ą┐čĆąŠą▓ąĄčĆčÅčéčī čĆąĄčłąĄąĮąĖčÅ ą┐ąĄčĆąĄą┤ ą┐čĆąĖą╝ąĄąĮąĄąĮąĖąĄą╝.

ąÆąŠąĘą╝ąŠąČąĮąŠ, čÅ ąĮąĄ čüą┤ąĄą╗ą░ą╗ čŹč鹊 čÅčüąĮčŗą╝ ą▓ čüą▓ąŠąĖčģ ą┐čĆąĄą┤čŗą┤čāčēąĖčģ čüąŠąŠą▒čēąĄąĮąĖčÅčģ, ąĮąŠ čÅ ą┐čĆąŠčłčā ą║ąŠąĮą║čĆąĄčéąĮąŠą╣ ą┐ąŠą╝ąŠčēąĖ ą┐ąŠ ą║ąŠąĮą║čĆąĄčéąĮąŠą╝čā ą▓ąŠą┐čĆąŠčüčā.

ąĢčüą╗ąĖ čā ą▓ą░čü ąĄčüčéčī ąŠą┐čŗčé ąĖą╗ąĖ ąĘąĮą░ąĮąĖčÅ, ą║ąŠč鹊čĆčŗąĄ ą╝ąŠą│čāčé ą┐ąŠą╝ąŠčćčī ą╝ąĮąĄ čĆąĄčłąĖčéčī čŹčéčā ą┐čĆąŠą▒ą╗ąĄą╝čā, čÅ ą▒čŗą╗ ą▒čŗ ąŠč湥ąĮčī ą▒ą╗ą░ą│ąŠą┤ą░čĆąĄąĮ ąĘą░ čŹč鹊. ąĢčüą╗ąĖ ąĮąĄčé, č鹊 ąĘą░č湥ą╝ ą╗ąĖčéčī ą▓ąŠą┤čā ąĖ čāčüčéčĆą░ąĖą▓ą░čéčī ą▒ąĄčüą┐ąŠą╗ąĄąĘąĮčāčÄ ą┐ąŠą╗ąĄą╝ąĖą║čā?

ąĪąĖčéčāą░čåąĖčÅ čü ą▓ą░ą╝ąĖ ąĮą░ą┐ąŠą╝ąĖąĮą░ąĄčé ąŠą▒čēąĄąĮąĖąĄ ąĮą░ č乊čĆčāą╝ąĄ:

ą×ą▒čŗčćąĮčŗą╣ ą┐ąŠą╗čīąĘąŠą▓ą░č鹥ą╗čī >>ą¤ąŠą╝ąŠą│ąĖč鹥, ą┐ąŠąČą░ą╗čāą╣čüčéą░, čÅ ąĮąĄ ą╝ąŠą│čā ąĘą░ą┐čāčüčéąĖčéčī čŹčéčā ą┐čĆąŠą│čĆą░ą╝ą╝čā, čćč鹊 ą╝ąĮąĄ ą┤ąĄą╗ą░čéčī?

"ą¤čĆąŠč乥čüčüąĖąŠąĮą░ą╗" >>ąÆčŗą║ąĖąĮčī ą║ąŠą╝ą┐!

ąÆą╗ąŠąČąĄąĮąĖčÅ:

ad.pdf [156.91 KiB]

ąĪą║ą░čćąĖą▓ą░ąĮąĖą╣: 50

ąÆąĄčĆąĮčāčéčīčüčÅ ąĮą░ą▓ąĄčĆčģ

>TEHb<

ąŚą░ą│ąŠą╗ąŠą▓ąŠą║ čüąŠąŠą▒čēąĄąĮąĖčÅ: Re: stm32+AD9238. High-speed ADC. ąÜą░ąĮą░ą╗čŗ ąÉ ąĖ ąæ. ąØą░čüčéčĆąŠą╣ą║ą░ DM

ąöąŠą▒ą░ą▓ą╗ąĄąĮąŠ: ą¤čé ą░ą▓ą│ 04, 2023 23:15:36

ąöčĆčāą│ ąÜąŠčéą░

ąÜą░čĆą╝ą░: 13

ąĀąĄą╣čéąĖąĮą│ čüąŠąŠą▒čēąĄąĮąĖą╣: 359

ąŚą░čĆąĄą│ąĖčüčéčĆąĖčĆąŠą▓ą░ąĮ: ąĪčĆ ąĮąŠčÅ 11, 2009 17:19:30ąĪąŠąŠą▒čēąĄąĮąĖą╣: 4323ą×čéą║čāą┤ą░: ąÆąŠčĆąŠąĮąĄąČ

ąĀąĄą╣čéąĖąĮą│ čüąŠąŠą▒čēąĄąĮąĖčÅ: 0

ąöąŠ ą║ąŠąĮčåą░ ąĮąĄ ą┤ąŠą┤čāą╝ą░ą╗, ąĮąŠ ą┐ąŠą║ą░ čüą┐ą░čéčī ąĮąĄ čāčłčæą╗ ąĮą░ą┐ąĖčłčā čćč鹊 ą┐ąŠąĮčÅą╗. ąöą╗čÅ ąĘą░ą║čĆąĄą┐ą╗ąĄąĮąĖčÅ, čéą░ą║ čüą║ą░ąĘą░čéčī.

ąÆ ąĖąĮčüčéčĆčāą║čåąĖąĖ ąĮą░ ąÉą”ą¤ ąĮą░ą┐ąĖčüą░ąĮąŠ, čćč鹊

ą”ąĖčéą░čéą░:

If the ADCs are run with synchronized timing, this same clock can

ą×č湥ą▓ąĖą┤ąĮąŠ, čŹč鹊 ą║ą░ą║ čĆą░ąĘ ąČąĄą╗ą░ąĄą╝ą░čÅ čüąĖčéčāą░čåąĖčÅ. ąóąŠ ąĄčüčéčī ąĘą░ ąŠą┤ąĖąĮ ą┐ąĄčĆąĖąŠą┤ čéą░ą║čéąĖčĆąŠą▓ą░ąĮąĖčÅ ą┤ą░ąĮąĮčŗąĄ ą▓čŗčüąŠą▓čŗą▓ą░čÄčéčüčÅ č鹊 ąŠą┤ąĮąĖ, č鹊 ą┤čĆčāą│ąĖąĄ. ąÉ ąĖąĮč鹥čĆč乥ą╣čü čüčćąĖčéčŗą▓ą░ąĄčé č鹊ą╗čīą║ąŠ ąŠą┤ąĖąĮ čĆą░ąĘ ąĘą░ ą┐ąĄčĆąĖąŠą┤, ą┐čĆąĖčćčæą╝ čüčĆą░ąĘčā ą┐ąŠ ąĘą░ą┤ąĮąĄą╝čā čäčĆąŠąĮčéčā (ą┐ąŠ čüą┐ą░ą┤čā). ąÉ čāąČ čāčüą┐ąĄą╗ čéą░ą╝ ąÉą”ą¤ ą┤ą░ąĮąĮčŗąĄ ą▓čŗčüčéą░ą▓ąĖčéčī ąĖą╗ąĖ ąĮąĄčé čŹč鹊 čāąČąĄ ąĄą│ąŠ ą┐čĆąŠą▒ą╗ąĄą╝čŗ.

ąÆąĄčĆąĮčāčéčīčüčÅ ąĮą░ą▓ąĄčĆčģ

dimaib

ąŚą░ą│ąŠą╗ąŠą▓ąŠą║ čüąŠąŠą▒čēąĄąĮąĖčÅ: Re: stm32+AD9238. High-speed ADC. ąÜą░ąĮą░ą╗čŗ ąÉ ąĖ ąæ. ąØą░čüčéčĆąŠą╣ą║ą░ DM

ąöąŠą▒ą░ą▓ą╗ąĄąĮąŠ: ą¤čé ą░ą▓ą│ 04, 2023 23:34:11

ą¤ąĄčĆą▓čŗą╣ čĆą░ąĘ čüą║ą░ąĘą░ą╗ ą£čÅčā!

ąŚą░čĆąĄą│ąĖčüčéčĆąĖčĆąŠą▓ą░ąĮ: ąĪą▒ ą░ą┐čĆ 02, 2011 04:05:00ąĪąŠąŠą▒čēąĄąĮąĖą╣: 33

ąĀąĄą╣čéąĖąĮą│ čüąŠąŠą▒čēąĄąĮąĖčÅ: 0

ą”ąĖčéą░čéą░:

ą×č湥ą▓ąĖą┤ąĮąŠ, čŹč鹊 ą║ą░ą║ čĆą░ąĘ ąČąĄą╗ą░ąĄą╝ą░čÅ čüąĖčéčāą░čåąĖčÅ. ąóąŠ ąĄčüčéčī ąĘą░ ąŠą┤ąĖąĮ ą┐ąĄčĆąĖąŠą┤ čéą░ą║čéąĖčĆąŠą▓ą░ąĮąĖčÅ ą┤ą░ąĮąĮčŗąĄ ą▓čŗčüąŠą▓čŗą▓ą░čÄčéčüčÅ č鹊 ąŠą┤ąĮąĖ, č鹊 ą┤čĆčāą│ąĖąĄ. ąÉ ąĖąĮč鹥čĆč乥ą╣čü čüčćąĖčéčŗą▓ą░ąĄčé č鹊ą╗čīą║ąŠ ąŠą┤ąĖąĮ čĆą░ąĘ ąĘą░ ą┐ąĄčĆąĖąŠą┤, ą┐čĆąĖčćčæą╝ čüčĆą░ąĘčā ą┐ąŠ ąĘą░ą┤ąĮąĄą╝čā čäčĆąŠąĮčéčā (ą┐ąŠ čüą┐ą░ą┤čā). ąÉ čāąČ čāčüą┐ąĄą╗ čéą░ą╝ ąÉą”ą¤ ą┤ą░ąĮąĮčŗąĄ ą▓čŗčüčéą░ą▓ąĖčéčī ąĖą╗ąĖ ąĮąĄčé čŹč鹊 čāąČąĄ ąĄą│ąŠ ą┐čĆąŠą▒ą╗ąĄą╝čŗ.

ąöą░, ą┤ą░.. ąĖą╝ąĄąĮąŠ ą┐ąŠčŹč鹊ą╝čā ą┐čĆąĖčłą╗ąŠčüčī ąĖčüą┐ąŠą╗čīąĘąŠą▓ą░čéčī ą┤čĆčāą│ąŠą╣ ąĖčüč鹊čćąĮąĖą║ čéą░ą║čéąĖčĆąŠą▓ą░ąĮąĖčÅ ą┤ą╗čÅ ąÉą”ą¤ ąĖ ą┐ąŠą┤ąĄą╗ąĖčéčī ąĄą│ąŠ čćą░čéčüąŠčéčā ąĮą░ 2, čćč鹊 ą▒čŗ ąĖąĮč鹥čĆč乥ą╣čü čüčćąĖčéčŗą▓ą░ą╗ ą┤ą░ąĮąĮčŗąĄ ą┤ą▓ą░ čĆą░ąĘą░ ąĘą░ ąŠą┤ąĖąĮ ą┐ąĄčĆąĖąŠą┤ čéą░ą║čéąĖčĆąŠą▓ą░ąĮąĖčÅ ąÉą”ą¤. ąØąŠ čüąĖąĮčģčĆąŠąĮąĖąĘąĖčĆąŠą▓ą░čéčī čŹč鹊 ąĮąĄ ą┐ąŠą╗čāčćą░ąĄčéčüčÅ.

ąśą╗ąĖ čÅ ąĮąĄ čāą╗ą░ą▓ą╗ąĖą▓ą░čÄ ą▓ą░čłčā ą╝čŗčüą╗čī?

ąÆąĄčĆąĮčāčéčīčüčÅ ąĮą░ą▓ąĄčĆčģ

ąĪčéčĆą░ąĮąĖčåą░ 1 ąĖąĘ 2

[ ąĪąŠąŠą▒čēąĄąĮąĖą╣: 31 ]

,

ąÜč鹊 čüąĄą╣čćą░čü ąĮą░ č乊čĆčāą╝ąĄ

ąĪąĄą╣čćą░čü čŹč鹊čé č乊čĆčāą╝ ą┐čĆąŠčüą╝ą░čéčĆąĖą▓ą░čÄčé: ąĮąĄčé ąĘą░čĆąĄą│ąĖčüčéčĆąĖčĆąŠą▓ą░ąĮąĮčŗčģ ą┐ąŠą╗čīąĘąŠą▓ą░č鹥ą╗ąĄą╣ ąĖ ą│ąŠčüčéąĖ: 29

ąÆčŗ ąĮąĄ ą╝ąŠąČąĄč鹥 ąĮą░čćąĖąĮą░čéčī č鹥ą╝čŗąĮąĄ ą╝ąŠąČąĄč鹥 ąŠčéą▓ąĄčćą░čéčī ąĮą░ čüąŠąŠą▒čēąĄąĮąĖčÅąĮąĄ ą╝ąŠąČąĄč鹥 čĆąĄą┤ą░ą║čéąĖčĆąŠą▓ą░čéčī čüą▓ąŠąĖ čüąŠąŠą▒čēąĄąĮąĖčÅąĮąĄ ą╝ąŠąČąĄč鹥 čāą┤ą░ą╗čÅčéčī čüą▓ąŠąĖ čüąŠąŠą▒čēąĄąĮąĖčÅąĮąĄ ą╝ąŠąČąĄč鹥 ą┤ąŠą▒ą░ą▓ą╗čÅčéčī ą▓ą╗ąŠąČąĄąĮąĖčÅ

, ą▓čüčæ ą┤ąŠą╗ąČąĮąŠ čĆą░ą▒ąŠčéą░čéčī ą║ą░ą║ čćą░čüčŗ

, ą▓čüčæ ą┤ąŠą╗ąČąĮąŠ čĆą░ą▒ąŠčéą░čéčī ą║ą░ą║ čćą░čüčŗ

, ą░ č鹊ą╗čīą║ąŠ ą┐ąŠč鹊ą╝ ąĮą░čćąĖąĮą░ąĄčé ą┤čāą╝ą░čéčī, ą║ą░ą║ ą┐čĆą░ą▓ąĖą╗ąŠ - ąĖą╗ąĖ čŹčéą░ ą┐ą░čĆčéąĖčÅ ąĖą┤čæčé ą▓ ą╝čāčüąŠčĆąĮčāčÄ ą║ąŠčƹʹĖąĮčā; ąĖą╗ąĖ ą┤ąŠą╗ą│ąŠ ąĖ ą╝čāčćąĖč鹥ą╗čīąĮąŠ ą┐ąŠč鹊ą╝ ą║ąŠčüčéčŗą╗ąĖčéčüčÅ, čćč鹊ą▒čŗ čģąŠčéčī ą║ą░ą║-č鹊 ą┤ąŠčéčÅąĮčāčéčī ą┤ąŠ čéčĆąĄą▒ąŠą▓ą░ąĮąĖą╣ (č湥ą│ąŠ ąŠą▒čŗčćąĮąŠ ąĮąĄ ą┐ąŠą╗čāčćą░ąĄčéčüčÅ, ą░ ąŠčüčéą░čæčéčüčÅ "čćč鹊 ą┐ąŠą╗čāčćąĖą╗ąŠčüčī").

, ą░ č鹊ą╗čīą║ąŠ ą┐ąŠč鹊ą╝ ąĮą░čćąĖąĮą░ąĄčé ą┤čāą╝ą░čéčī, ą║ą░ą║ ą┐čĆą░ą▓ąĖą╗ąŠ - ąĖą╗ąĖ čŹčéą░ ą┐ą░čĆčéąĖčÅ ąĖą┤čæčé ą▓ ą╝čāčüąŠčĆąĮčāčÄ ą║ąŠčƹʹĖąĮčā; ąĖą╗ąĖ ą┤ąŠą╗ą│ąŠ ąĖ ą╝čāčćąĖč鹥ą╗čīąĮąŠ ą┐ąŠč鹊ą╝ ą║ąŠčüčéčŗą╗ąĖčéčüčÅ, čćč鹊ą▒čŗ čģąŠčéčī ą║ą░ą║-č鹊 ą┤ąŠčéčÅąĮčāčéčī ą┤ąŠ čéčĆąĄą▒ąŠą▓ą░ąĮąĖą╣ (č湥ą│ąŠ ąŠą▒čŗčćąĮąŠ ąĮąĄ ą┐ąŠą╗čāčćą░ąĄčéčüčÅ, ą░ ąŠčüčéą░čæčéčüčÅ "čćč鹊 ą┐ąŠą╗čāčćąĖą╗ąŠčüčī").