|

–§–æ—Ä—É–º –Ý–∞–¥–∏–æ–ö–æ—Ç • –ü—Ä–æ—Å–º–æ—Ç—Ä —Ç–µ–º—ã - –ò–Ω–∏—Ü–∏–∞–ª–∏–∑–∏—Ä–æ–≤–∞—Ç—å —Ä–µ–≥–∏—Å—Ç—Ä 74HC595N

–°–æ–æ–±—â–µ–Ω–∏—è –±–µ–∑ –æ—Ç–≤–µ—Ç–æ–≤ | –ê–∫—Ç–∏–≤–Ω—ã–µ —Ç–µ–º—ã

|

–°—Ç—Ä–∞–Ω–∏—Ü–∞ 1 –∏–∑ 3

|

[ –°–æ–æ–±—â–µ–Ω–∏–π: 42 ] |

, , |

| –ê–≤—Ç–æ—Ä |

–°–æ–æ–±—â–µ–Ω–∏–µ |

KorbenDallas

|

–ó–∞–≥–æ–ª–æ–≤–æ–∫ —Å–æ–æ–±—â–µ–Ω–∏—è: –ò–Ω–∏—Ü–∏–∞–ª–∏–∑–∏—Ä–æ–≤–∞—Ç—å —Ä–µ–≥–∏—Å—Ç—Ä 74HC595N  –î–æ–±–∞–≤–ª–µ–Ω–æ: –î–æ–±–∞–≤–ª–µ–Ω–æ: –í—Ç —Ñ–µ–≤ 02, 2021 23:25:01 |

|

| –í—Å—Ç–∞–ª –Ω–∞ –ª–∞–ø—ã |

|

–ö–∞—Ä–º–∞: 1

–Ý–µ–π—Ç–∏–Ω–≥ —Å–æ–æ–±—â–µ–Ω–∏–π: -1

–ó–∞—Ä–µ–≥–∏—Å—Ç—Ä–∏—Ä–æ–≤–∞–Ω: –ü–Ω –æ–∫—Ç 31, 2016 06:23:19

–°–æ–æ–±—â–µ–Ω–∏–π: 93

–Ý–µ–π—Ç–∏–Ω–≥ —Å–æ–æ–±—â–µ–Ω–∏—è: 0

|

|

–ó–∞–¥–∞—á–∞ —Ç–∞–∫–∞—è:

1. –£ –Ω–∞—Å –µ—Å—Ç—å —Å–¥–≤–∏–≥–æ–≤—ã–π —Ä–µ–≥–∏—Å—Ç—Ä 74HC595N. –≠—Ç–æ—Ç —Ä–µ–≥–∏—Å—Ç—Ä –∑–∞—Ü–∏–∫–ª–µ–Ω —Å–∞–º –Ω–∞ —Å–µ–±—è, —Ç–æ –µ—Å—Ç—å –ø–æ —Å–∏–≥–Ω–∞–ª—É —Ç–∞–∫—Ç–æ–≤–æ–≥–æ –≥–µ–Ω–µ—Ä–∞—Ç–æ—Ä–∞ –≥–æ–Ω—è–µ—Ç –ø–æ –∫—Ä—É–≥—É –Ω–µ–∫–∏–π 8-–±–∏—Ç–Ω—ã–π –Ω–∞–±–æ—Ä.

2. –í –∫–∞—á–µ—Å—Ç–≤–µ —Ç–∞–∫—Ç–æ–≤–æ–≥–æ –≥–µ–Ω–µ—Ä–∞—Ç–æ—Ä–∞ –∏—Å–ø–æ–ª—å–∑—É–µ—Ç—Å—è –≥–µ–Ω–µ—Ä–∞—Ç–æ—Ä –ø—Ä—è–º–æ—É–≥–æ–ª—å–Ω—ã—Ö –∏–º–ø—É–ª—å—Å–æ–≤ –Ω–∞ –±–∞–∑–µ 555 —Ç–∞–π–º–µ—Ä–∞.

–¢–µ–æ—Ä–µ—Ç–∏—á–µ—Å–∫–∏ –±–∏—Ç–æ–≤—ã–π –Ω–∞–±–æ—Ä –≤ —Ä–µ–≥–∏—Å—Ç—Ä–µ –º–æ–∂–µ—Ç –±—ã—Ç—å –ª—é–±—ã–º. –ù–æ —Ö–æ—Ç–µ–ª–æ—Å—å –±—ã —á—Ç–æ–±—ã –ø—Ä–∏ –ø–æ–¥–∞—á–µ –ø–∏—Ç–∞–Ω–∏—è –∑–Ω–∞—á–µ–Ω–∏–µ –≤ —Ä–µ–≥–∏—Å—Ç—Ä–µ –∏–Ω–∏—Ü–∏–∞–ª–∏–∑–∏—Ä–æ–≤–∞–ª–æ—Å—å –æ–¥–∏–Ω–æ–∫–æ–π –µ–¥–∏–Ω–∏—Ü–µ–π. –¢–æ –µ—Å—Ç—å —á—Ç–æ–±—ã "–ø–æ —É–º–æ–ª—á–∞–Ω–∏—é" –ø–æ—Å–ª–µ –≤–∫–ª—é—á–µ–Ω–∏—è –ø–∏—Ç–∞–Ω–∏—è —Ä–µ–≥–∏—Å—Ç—Ä —Å—Ä–∞–∑—É –Ω–∞—á–∏–Ω–∞–ª –≥–æ–Ω—è—Ç—å –ø–æ –∫—Ä—É–≥—É –æ–¥–∏–Ω–æ–∫—É—é –µ–¥–∏–Ω–∏—Ü—É.

–ö–∞–∫ –ø—Ä–æ—â–µ –≤—Å–µ–≥–æ —Å–¥–µ–ª–∞—Ç—å —Ç–∞–∫—É—é –∏–Ω–∏—Ü–∏–∞–ª–∏–∑–∞—Ü–∏—é –¥–ª—è 74HC595N?

|

|

| –í–µ—Ä–Ω—É—Ç—å—Å—è –Ω–∞–≤–µ—Ä—Ö |

|

|

|

–Ý–µ–∫–ª–∞–º–∞

|

|

|

|

|

|

|

|

|

74LS00

|

–ó–∞–≥–æ–ª–æ–≤–æ–∫ —Å–æ–æ–±—â–µ–Ω–∏—è: Re: –ò–Ω–∏—Ü–∏–∞–ª–∏–∑–∏—Ä–æ–≤–∞—Ç—å —Ä–µ–≥–∏—Å—Ç—Ä 74HC595N  –î–æ–±–∞–≤–ª–µ–Ω–æ: –î–æ–±–∞–≤–ª–µ–Ω–æ: –ß—Ç —Ñ–µ–≤ 04, 2021 19:36:20 |

|

–ö–∞—Ä–º–∞: -8

–Ý–µ–π—Ç–∏–Ω–≥ —Å–æ–æ–±—â–µ–Ω–∏–π: 15

–ó–∞—Ä–µ–≥–∏—Å—Ç—Ä–∏—Ä–æ–≤–∞–Ω: –í—Å –∏—é–ª 24, 2011 11:38:09

–°–æ–æ–±—â–µ–Ω–∏–π: 7634

–Ý–µ–π—Ç–∏–Ω–≥ —Å–æ–æ–±—â–µ–Ω–∏—è: 0

|

|

–ü—Ä–æ—â–µ –≤—Å–µ–≥–æ –≤–∑—è—Ç—å –ú–ö –∏ –≤—ã–∫–∏–Ω—É—Ç—å —Ä–µ–≥–∏—Å—Ç—Ä, –±—É–¥—É—Ç —Å—Ö–µ–º–∞ –ø—Ä–æ—â–µ –∏ –Ω–∞ –æ–¥–Ω–æ–π –¥–µ—Ç–∞–ª–µ.

–ê —Ç–æ –±—ã –≤—Å–µ —É–∂–µ —Å–¥–µ–ª–∞–ª–∏ —Ç–∞–∫—É—é —à—Ç—É–∫–æ–≤–∏–Ω—É —á—Ç–æ–± 1307 –∑–∞—Å—Ç–∞–≤–∏—Ç—å —Å–µ–∫—É–Ω–¥–Ω—ã–º –≥–µ–Ω–µ—Ä–∞—Ç–æ—Ä–æ–º –≤—Ä–æ–¥–µ –ò–ï5 –∏ —Å—Ç–∞–≤–∏–ª–∏ –±—ã –≤ —á–∞—Å–∏–∫–∏ –Ω–∞ —Ä–∞—Å—Å—ã–ø—É—Ö—É. –ù–æ —á—Ç–æ—Ç–æ –ø–æ–∫–∞ –Ω–∏–∫—Ç–æ –Ω–µ —Å–º–æ–≥, –∏ –≤—Å–µ —Å–æ–±–∏—Ä–∞—é—Ç –Ω–∞ –ú–ö.

–î–µ—Ç–∞–ª—é—à–µ–∫ –Ω–∞–¥–æ –Ω–µ –º–µ–Ω—å—à–µ —á–µ–º –ª–æ–≥–∏–∫–∏ –≤ —Å–∞–º–æ–º 595.

–ü–æ–¥—Ç—è–Ω—É—Ç—å –≤—Ö–æ–¥—ã –∫ –Ω—É–ª—é —á—Ç–æ —É–∂–µ –Ω–µ –ø—Ä–∞–≤–∏–ª—å–Ω–æ.

–ò —Å–¥–µ–ª–∞—Ç—å –ª–æ–≥–∏–∫—É —É—Å—Ç–∞–Ω–æ–≤–∫–∏ –µ–¥–∏–Ω–∏—Ü—ã —Å –ø–æ—Å–ª–µ–¥—É—é—â–µ–π –∑–∞–ø–∏—Å—å—é –∏ —Ä–∞–±–æ—á–∏–º —Ä–µ–∂–∏–º–æ–º, –∏ –ª–æ–≥–∏–∫—É –æ—Ç–≤—è–∑–∫–∏ —á—Ç–æ —Ä–µ–≥–∏—Å—Ç—Ä –ø—Ä–æ–¥–æ–ª–∂–∏—Ç—å —Ä–∞–±–æ—Ç–∞—Ç—å –∫–∞–∫ –æ–±—ã—á–Ω—ã–π, –æ—Ç–∫–ª—é—á–∞—é—â–∏–π –ø–µ—Ä–≤—ã–π –∫–æ—Å—Ç—ã–ª—å –¥–æ –æ—Ç–∫–ª—é—á–µ–Ω–∏—è –ø–∏—Ç–∞–Ω–∏—è

|

|

| –í–µ—Ä–Ω—É—Ç—å—Å—è –Ω–∞–≤–µ—Ä—Ö |

|

|

|

–Ý–µ–∫–ª–∞–º–∞

|

|

|

|

|

|

|

|

|

BOB51

|

–ó–∞–≥–æ–ª–æ–≤–æ–∫ —Å–æ–æ–±—â–µ–Ω–∏—è: Re: –ò–Ω–∏—Ü–∏–∞–ª–∏–∑–∏—Ä–æ–≤–∞—Ç—å —Ä–µ–≥–∏—Å—Ç—Ä 74HC595N  –î–æ–±–∞–≤–ª–µ–Ω–æ: –î–æ–±–∞–≤–ª–µ–Ω–æ: –ü—Ç —Ñ–µ–≤ 05, 2021 10:57:40 |

|

| –î—Ä—É–≥ –ö–æ—Ç–∞ |

|

–ö–∞—Ä–º–∞: 96

–Ý–µ–π—Ç–∏–Ω–≥ —Å–æ–æ–±—â–µ–Ω–∏–π: 1502

–ó–∞—Ä–µ–≥–∏—Å—Ç—Ä–∏—Ä–æ–≤–∞–Ω: –í—Ç –º–∞—Ä 16, 2010 22:02:27

–°–æ–æ–±—â–µ–Ω–∏–π: 15453

–û—Ç–∫—É–¥–∞: –î–û–ù–ï–¶–ö

–Ý–µ–π—Ç–∏–Ω–≥ —Å–æ–æ–±—â–µ–Ω–∏—è: 0

|

595–π –¥–ª—è —Ç–∞–∫–∏—Ö —Ü–µ–ª–µ–π –Ω–µ –ø–æ–¥—Ö–æ–¥–∏—Ç. –î–ª—è –ø—Ä–µ–¥–≤–∞—Ä–∏—Ç–µ–ª—å–Ω–æ–π –∏–Ω–∏—Ü–∏–∞–ª–∏–∑–∞—Ü–∏–∏ –ø—Ä–æ–∏–∑–≤–æ–ª—å–Ω—ã–º –∫–æ–¥–æ–º –Ω—É–∂–µ–Ω –∫–æ–º–±–∏–Ω–∏—Ä–æ–≤–∞–Ω–Ω—ã–π —Ä–µ–≥–∏—Å—Ç—Ä —Å –≤–æ–∑–º–æ–∂–Ω–æ—Å—Ç—å—é –ø–∞—Ä–∞–ª–ª–µ–ª—å–Ω–æ–π –∑–∞–ø–∏—Å–∏ –¥–∞–Ω–Ω—ã—Ö. —á—Ç–æ-—Ç–æ –ø–æ—Ö–æ–∂–µ–µ –Ω–∞ –ö176–ò–Ý6 (IW4034B http://tec.org.ru/_bd/35/3572_IW4034Be.pdf ). –ù–æ —Ç–∞–º –Ω–∞ "—Ä–∞—Å—Å—ã–ø—É—Ö–µ" –ø—Ä–∏–¥–µ—Ç—Å—è –ø–æ—Ç—Ä—É–¥–∏—Ç—å—Å—è —Å –∞–≤—Ç–æ–º–∞—Ç–æ–º —É–ø—Ä–∞–≤–ª–µ–Ω–∏—è (–∏–ª–∏ –ú–ö —Å—Ç–∞–≤–∏—Ç—å).

|

|

| –í–µ—Ä–Ω—É—Ç—å—Å—è –Ω–∞–≤–µ—Ä—Ö |

|

|

musor

|

–ó–∞–≥–æ–ª–æ–≤–æ–∫ —Å–æ–æ–±—â–µ–Ω–∏—è: Re: –ò–Ω–∏—Ü–∏–∞–ª–∏–∑–∏—Ä–æ–≤–∞—Ç—å —Ä–µ–≥–∏—Å—Ç—Ä 74HC595N  –î–æ–±–∞–≤–ª–µ–Ω–æ: –î–æ–±–∞–≤–ª–µ–Ω–æ: –ü—Ç —Ñ–µ–≤ 05, 2021 11:45:51 |

|

| –î—Ä—É–≥ –ö–æ—Ç–∞ |

|

–ö–∞—Ä–º–∞: 123

–Ý–µ–π—Ç–∏–Ω–≥ —Å–æ–æ–±—â–µ–Ω–∏–π: 7958

–ó–∞—Ä–µ–≥–∏—Å—Ç—Ä–∏—Ä–æ–≤–∞–Ω: –°–± —Å–µ–Ω 13, 2014 16:27:32

–°–æ–æ–±—â–µ–Ω–∏–π: 39197

–û—Ç–∫—É–¥–∞: –°–ø–∏—Ä—Ç–æ–ì–æ–Ω—Å–∫ —Å–æ–∑–≤–µ–∑–¥–∏—è –û–º–µ–≥–∞

–Ý–µ–π—Ç–∏–Ω–≥ —Å–æ–æ–±—â–µ–Ω–∏—è: 0

|

|

–Ω–µ–∫–æ–≥–¥–∞ –¥–µ–ª–∞–ª –∞–≤—Ç–º–∞—Ç —Å–≤–µ—Ç–æ—ç—Ñ–µ–∫—Ç–æ—Ñ –Ω–∞ 74—Ö—Ö175 –∫—É—á–∞ —Ä–µ–¥–∏–º–æ—Ñ –±—ã–ª–∞

_________________

Z–ú—É–¥—Ä–æ—Å—Ç—å(–û–ø—ã—Ç –∏ –≤—ã–¥–µ—Ä–∂–∫–∞) –ø—Ä–∏—Ö–æ–¥–∏—Ç —Å –≥–æ–¥–∞–º–∏.

–í—Å–µ –í–∞—à–∏ –±–µ–¥—ã –∏ –ø—Ä–æ–±–ª–µ–º—ã, –æ—Ç –Ω–µ–¥–æ—Å—Ç–∞—Ç–∫–∞ –∑–Ω–∞–Ω–∏–π.

–£–º–Ω—ã–π –∏ —É –¥—É—Ä–∞–∫–∞ –Ω–∞—É—á–∏—Ç—Å—è, –∞ –¥—É—Ä–∞–∫—É –∏ ..

–ê–ª–±–µ—Ä—Ç –ï–π–Ω—à—Ç–µ–π–Ω –Ω–µ –ø–æ–º–æ–∂–µ—Ç –∏ –í–í–ü –Ω–µ —Å–ø–∞—Å–µ—Ç.–∏ –ú–ß–° –æ–ø–∞–∑–¥–∞–µ—Ç

|

|

| –í–µ—Ä–Ω—É—Ç—å—Å—è –Ω–∞–≤–µ—Ä—Ö |

|

|

|

–Ý–µ–∫–ª–∞–º–∞

|

|

|

|

|

|

|

|

|

diplodok

|

–ó–∞–≥–æ–ª–æ–≤–æ–∫ —Å–æ–æ–±—â–µ–Ω–∏—è: Re: –ò–Ω–∏—Ü–∏–∞–ª–∏–∑–∏—Ä–æ–≤–∞—Ç—å —Ä–µ–≥–∏—Å—Ç—Ä 74HC595N  –î–æ–±–∞–≤–ª–µ–Ω–æ: –î–æ–±–∞–≤–ª–µ–Ω–æ: –ü—Ç —Ñ–µ–≤ 05, 2021 20:47:50 |

|

| –ì–æ–≤–æ—Ä—è—â–∏–π —Å —Ç–µ–∫—Å—Ç–æ–ª–∏—Ç–æ–º |

–ö–∞—Ä–º–∞: 20

–Ý–µ–π—Ç–∏–Ω–≥ —Å–æ–æ–±—â–µ–Ω–∏–π: 513

–ó–∞—Ä–µ–≥–∏—Å—Ç—Ä–∏—Ä–æ–≤–∞–Ω: –ß—Ç –∞–≤–≥ 10, 2017 20:57:51

–°–æ–æ–±—â–µ–Ω–∏–π: 1692

–Ý–µ–π—Ç–∏–Ω–≥ —Å–æ–æ–±—â–µ–Ω–∏—è: 0

|

–ü–æ—Å–ª–µ –ø–µ—Ä–≤–æ–≥–æ —Ç–∞–∫—Ç–∞ –¥–æ–ª–∂–Ω–∞ –ø–æ—è–≤–∏—Ç—Å—è 1. –°—Ö–µ–º—É –Ω–µ –¥–µ–ª–∞–ª

|

|

| –í–µ—Ä–Ω—É—Ç—å—Å—è –Ω–∞–≤–µ—Ä—Ö |

|

|

|

–Ý–µ–∫–ª–∞–º–∞

|

|

|

|

|

|

|

|

|

–ê–ª–µ–∫—Å–∞–Ω–¥—Ä–õ

|

–ó–∞–≥–æ–ª–æ–≤–æ–∫ —Å–æ–æ–±—â–µ–Ω–∏—è: Re: –ò–Ω–∏—Ü–∏–∞–ª–∏–∑–∏—Ä–æ–≤–∞—Ç—å —Ä–µ–≥–∏—Å—Ç—Ä 74HC595N  –î–æ–±–∞–≤–ª–µ–Ω–æ: –î–æ–±–∞–≤–ª–µ–Ω–æ: –ü—Ç —Ñ–µ–≤ 05, 2021 23:14:38 |

|

| –î—Ä—É–≥ –ö–æ—Ç–∞ |

|

–ö–∞—Ä–º–∞: 197

–Ý–µ–π—Ç–∏–Ω–≥ —Å–æ–æ–±—â–µ–Ω–∏–π: 8630

–ó–∞—Ä–µ–≥–∏—Å—Ç—Ä–∏—Ä–æ–≤–∞–Ω: –ü–Ω –Ω–æ—è 30, 2009 03:00:01

–°–æ–æ–±—â–µ–Ω–∏–π: 43467

–û—Ç–∫—É–¥–∞: –ù–µ—Ä–µ–∑–∏–Ω–æ–≤–∞—è

–Ý–µ–π—Ç–∏–Ω–≥ —Å–æ–æ–±—â–µ–Ω–∏—è: 0

|

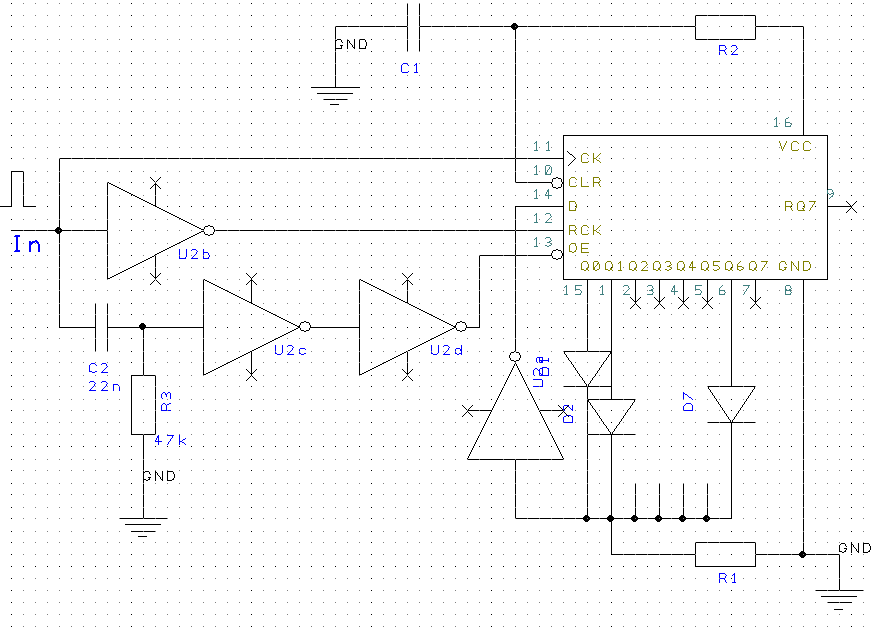

–ù–æ —Ö–æ—Ç–µ–ª–æ—Å—å –±—ã —á—Ç–æ–±—ã –ø—Ä–∏ –ø–æ–¥–∞—á–µ –ø–∏—Ç–∞–Ω–∏—è –∑–Ω–∞—á–µ–Ω–∏–µ –≤ —Ä–µ–≥–∏—Å—Ç—Ä–µ –∏–Ω–∏—Ü–∏–∞–ª–∏–∑–∏—Ä–æ–≤–∞–ª–æ—Å—å –æ–¥–∏–Ω–æ–∫–æ–π –µ–¥–∏–Ω–∏—Ü–µ–π. –¢–æ –µ—Å—Ç—å —á—Ç–æ–±—ã "–ø–æ —É–º–æ–ª—á–∞–Ω–∏—é" –ø–æ—Å–ª–µ –≤–∫–ª—é—á–µ–Ω–∏—è –ø–∏—Ç–∞–Ω–∏—è —Ä–µ–≥–∏—Å—Ç—Ä —Å—Ä–∞–∑—É –Ω–∞—á–∏–Ω–∞–ª –≥–æ–Ω—è—Ç—å –ø–æ –∫—Ä—É–≥—É –æ–¥–∏–Ω–æ–∫—É—é –µ–¥–∏–Ω–∏—Ü—É.

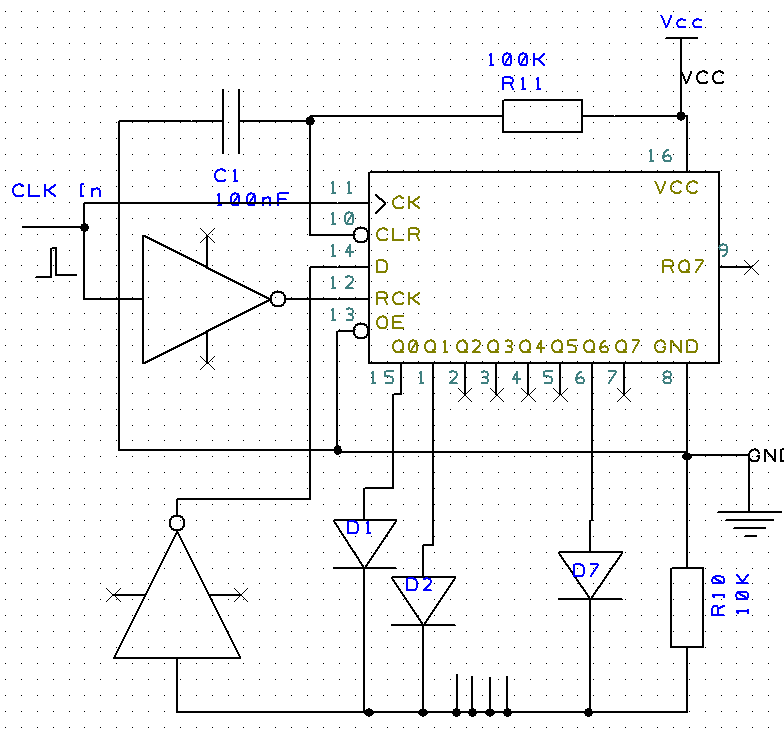

–ö–∞–∫ –ø—Ä–æ—â–µ –≤—Å–µ–≥–æ —Å–¥–µ–ª–∞—Ç—å —Ç–∞–∫—É—é –∏–Ω–∏—Ü–∏–∞–ª–∏–∑–∞—Ü–∏—é –¥–ª—è 74HC595N? –í–ª–æ–∂–µ–Ω–∏–µ:

–ë–µ–≥—É—â–∏–π –æ–≥–æ–Ω—å.png [65.71 KiB]

–°–∫–∞—á–∏–≤–∞–Ω–∏–π: 122

–ë–µ–≥—É—â–∏–π –æ–≥–æ–Ω—å.png [65.71 KiB]

–°–∫–∞—á–∏–≤–∞–Ω–∏–π: 122

–§–∞–π–ª –ø—Ä–æ—Ç–µ—É—Å–∞: –í–ª–æ–∂–µ–Ω–∏–µ:

–ë–µ–≥—É—â–∏–π –æ–≥–æ–Ω—å.zip [14.55 KiB]

–°–∫–∞—á–∏–≤–∞–Ω–∏–π: 139

–ë–µ–≥—É—â–∏–π –æ–≥–æ–Ω—å.zip [14.55 KiB]

–°–∫–∞—á–∏–≤–∞–Ω–∏–π: 139

–ù–µ–¥–æ—Å—Ç–∞—Ç–æ–∫ —ç—Ç–æ–π –ü–Ý–û–°–¢–ï–ô–®–ï–ô —Å—Ö–µ–º—ã - –Ω–µ–æ–±—Ö–æ–¥–∏–º–æ—Å—Ç—å –ø–æ–¥–±–æ—Ä–∞ –ø–∞—Ä–∞–º–µ—Ç—Ä–æ–≤ —Ü–µ–ø–æ—á–∫–∏ R4 C2 –≤ –∑–∞–≤–∏—Å–∏–º–æ—Å—Ç–∏ –æ—Ç —á–∞—Å—Ç–æ—Ç—ã, –≤—ã—Ä–∞–±–∞—Ç—ã–≤–∞–µ–º–æ–π 555 —Ç–∞–π–º–µ—Ä–æ–º- –µ—Å–ª–∏ –¥–ª–∏—Ç–µ–ª—å–Ω–æ—Å—Ç—å "—É—Å—Ç–∞–Ω–æ–≤–æ—á–Ω–æ–≥–æ –∏–º–ø—É–ª—å—Å–∞" –±—É–¥–µ—Ç –º–∞–ª–æ–π- —Ç–æ –Ω–∏—á–µ–≥–æ –Ω–µ –ø–æ–±–µ–∂–∏—Ç, –∞, –µ—Å–ª–∏ –±–æ–ª—å—à–æ–π- —Ç–æ –ø–æ–±–µ–∂–∏—Ç –¥–≤–µ –∑–≤—ë–∑–¥–æ—á–∫–∏, –∏–ª–∏ —Ç—Ä–∏ –∑–≤—ë–∑–¥–æ—á–∫–∏.. –õ—É—á—à–µ –≤—Å–µ–≥–æ, –∫–æ–Ω–µ—á–Ω–æ, –ø—è—Ç—å –∑–≤—ë–∑–¥–æ—á–µ–∫....     –°–ø–æ–π–ª–µ—Ä

|

|

| –í–µ—Ä–Ω—É—Ç—å—Å—è –Ω–∞–≤–µ—Ä—Ö |

|

|

|

–Ý–µ–∫–ª–∞–º–∞

|

|

|

|

|

|

|

|

|

KorbenDallas

|

–ó–∞–≥–æ–ª–æ–≤–æ–∫ —Å–æ–æ–±—â–µ–Ω–∏—è: Re: –ò–Ω–∏—Ü–∏–∞–ª–∏–∑–∏—Ä–æ–≤–∞—Ç—å —Ä–µ–≥–∏—Å—Ç—Ä 74HC595N  –î–æ–±–∞–≤–ª–µ–Ω–æ: –î–æ–±–∞–≤–ª–µ–Ω–æ: –ü—Ç —Ñ–µ–≤ 12, 2021 10:44:44 |

|

| –í—Å—Ç–∞–ª –Ω–∞ –ª–∞–ø—ã |

|

–ö–∞—Ä–º–∞: 1

–Ý–µ–π—Ç–∏–Ω–≥ —Å–æ–æ–±—â–µ–Ω–∏–π: -1

–ó–∞—Ä–µ–≥–∏—Å—Ç—Ä–∏—Ä–æ–≤–∞–Ω: –ü–Ω –æ–∫—Ç 31, 2016 06:23:19

–°–æ–æ–±—â–µ–Ω–∏–π: 93

–Ý–µ–π—Ç–∏–Ω–≥ —Å–æ–æ–±—â–µ–Ω–∏—è: 0

|

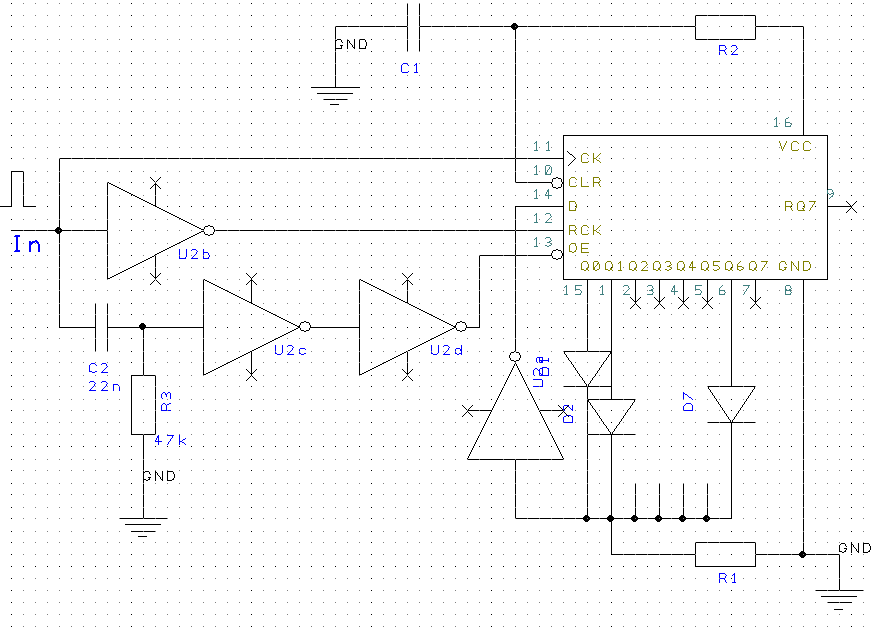

–Ø —Å–æ–æ—Ä—É–¥–∏–ª –Ω–µ—á—Ç–æ –±–æ–ª–µ–µ –Ω–∞–≤–æ—Ä–æ—á–µ–Ω–Ω–æ–µ —Å —Ç–µ–º–∏ –∂–µ –Ω–µ–¥–æ—Å—Ç–∞—Ç–∫–∞–º–∏  –î–ª—è –Ω–∞—á–∞–ª–∞ —è —Å–æ–±—Ä–∞–ª –∫–æ–º–±–∏–Ω–∞—Ü–∏—é –∏–∑ –¥–≤—É—Ö —Ä–µ–∑–∏—Å—Ç–æ—Ä–æ–≤, –¥–≤—É—Ö –∫–æ–Ω–¥–µ–Ω—Å–∞—Ç–æ—Ä–æ–≤ –∏ –¥–∏–æ–¥–∞ –¥–ª—è –≥–µ–Ω–µ—Ä–∞—Ü–∏–∏ –∞–Ω–∞–ª–æ–≥–æ–≤–æ–≥–æ V-–æ–±—Ä–∞–∑–Ω–æ–≥–æ —Å–∏–≥–Ω–∞–ª–∞, –∫–æ—Ç–æ—Ä—ã–π –ø—Ä–æ–≤–∞–ª–∏–≤–∞–µ—Ç—Å—è –Ω–∏–∂–µ 1/3 Vcc, –∫–∞–∫ –ø–æ–∫–∞–∑–∞–Ω–æ –∑–¥–µ—Å—å. –≠—Ç–∞ –∞–Ω–∞–ª–æ–≥–æ–≤–∞—è "–≥–∞–ª–æ—á–∫–∞" –∏–¥–µ—Ç –Ω–∞ –≤—Ö–æ–¥—ã –¥–≤—É—Ö 555, —Å–∫–æ–Ω—Ñ–∏–≥—É—Ä–∏—Ä–æ–≤–∞–Ω–Ω—ã—Ö –≤ –æ–¥–Ω–æ–≤–∏–±—Ä–∞—Ç–æ—Ä—ã: –∫–æ—Ä–æ—Ç–∫–∏–π –∏–º–ø—É–ª—å—Å –∏ –¥–ª–∏–Ω–Ω—ã–π –∏–º–ø—É–ª—å—Å. –í—ã—Ö–æ–¥ –ø–µ—Ä–≤–æ–≥–æ –æ–¥–Ω–æ–≤–∏–±—Ä–∞—Ç–æ—Ä–∞ (–∫–æ—Ä–æ—Ç–∫–∏–π) —á–µ—Ä–µ–∑ –∏–Ω–≤–µ—Ä—Ç–µ—Ä –ø–æ–¥–∞–µ—Ç—Å—è –Ω–∞ –≤—Ö–æ–¥ SRCLR —Ä–µ–≥–∏—Å—Ç—Ä–∞ - —ç—Ç–æ –Ω–∞—á–∞–ª—å–Ω–∞—è –æ—á–∏—Å—Ç–∫–∞ —Ä–µ–≥–∏—Å—Ç—Ä–∞ –ø–æ—Å–ª–µ –≤–∫–ª—é—á–µ–Ω–∏—è –ø–∏—Ç–∞–Ω–∏—è. –í—Ç–æ—Ä–æ–π –æ–¥–Ω–æ–≤–∏–±—Ä–∞—Ç–æ—Ä (–¥–ª–∏–Ω–Ω—ã–π) –≥–µ–Ω–µ—Ä–∏—Ä—É–µ—Ç –±–æ–ª–µ–µ –¥–ª–∏—Ç–µ–ª—å–Ω—ã–π –∏–º–ø—É–ª—å—Å, –∫–æ—Ç–æ—Ä—ã–π –ø–æ–¥–∞–µ—Ç—Å—è –Ω–∞ –≤—Ö–æ–¥ –¥–∞–Ω–Ω—ã—Ö SER —Ä–µ–≥–∏—Å—Ç—Ä–∞. –≠—Ç–æ—Ç –∏–º–ø—É–ª—å—Å –¥–æ–ª–∂–µ–Ω –ø—Ä–∏–∑–≤–∞–Ω "–Ω–∞–∫—Ä—ã—Ç—å" —Ä–æ–≤–Ω–æ –æ–¥–∏–Ω –ø–æ–ª–æ–∂–∏—Ç–µ–ª—å–Ω—ã–π —Ñ—Ä–æ–Ω—Ç —Ç–∞–∫—Ç–æ–≤–æ–≥–æ –≥–µ–Ω–µ—Ä–∞—Ç–æ—Ä–∞ (–ø–æ—Å–ª–µ –æ—Ç—Ä–∞–±–æ—Ç–∫–∏ –æ—á–∏—Å—Ç–∫–∏) - —ç—Ç–æ –±—É–¥–µ—Ç –Ω–∞—à–∞ –µ–¥–∏–Ω—Å—Ç–≤–µ–Ω–Ω–∞—è –≤—Ö–æ–¥—è—â–∞—è –µ–¥–∏–Ω–∏—Ü–∞. –ü–æ—Å–ª–µ –ø–æ–¥–±–æ—Ä–∞ –Ω–æ–º–∏–Ω–∞–ª–æ–≤ –ø–æ–ª—É—á–∞–µ–º  - –ê–Ω–∞–ª–æ–≥–æ–≤—ã–π V-–æ–±—Ä–∞–∑–Ω—ã–π —Å–∏–≥–Ω–∞–ª - –í—ã—Ö–æ–¥ 555, –æ–±–µ—Å–ø–µ—á–∏–≤–∞—é—â–µ–≥–æ SRCLR (–¥–æ –∏–Ω–≤–µ—Ä—Ç–µ—Ä–∞) - –í—ã—Ö–æ–¥ 555, –æ–±–µ—Å–ø–µ—á–∏–≤–∞—é—â–µ–≥–æ –µ–¥–∏–Ω–∏—Ü—É –Ω–∞ SER - –í—ã—Ö–æ–¥ 555, –≥–µ–Ω–µ—Ä–∏—Ä—É—é—â–µ–≥–æ —Ç–∞–∫—Ç–æ–≤—ã–µ –∏–º–ø—É–ª—å—Å—ã –¥–ª—è —Ä–µ–≥–∏—Å—Ç—Ä–∞ –ö–∞–∫ –≤–∏–¥–∏—Ç–µ, –º–∞–ª–∏–Ω–æ–≤—ã–π SER –∏–º–ø—É–ª—å—Å –Ω–∞–∫—Ä—ã–≤–∞–µ—Ç —Ç–æ–ª—å–∫–æ –æ–¥–∏–Ω —Ñ—Ä–æ–Ω—Ç —Å–∏–Ω–∏—Ö —Ç–∞–∫—Ç–æ–≤—ã—Ö –∏–º–ø—É–ª—å—Å–æ–≤ –ø–æ—Å–ª–µ –æ—Ç—Ä–∞–±–æ—Ç–∫–∏ –≥–æ–ª—É–±–æ–≥–æ SRCLR –∏–º–ø—É–ª—å—Å–∞. –•–æ—Ç—è –Ω–∞–¥–æ —Å–¥–µ–ª–∞—Ç—å –º–∞–ª–∏–Ω–æ–≤—ã–π –ø–æ–∫–æ—Ä–æ—á–µ, –∏–±–æ –º–æ–∂–µ—Ç –Ω–∞–∫—Ä—ã—Ç—å –∏ –¥–≤–∞. –í—Å–µ —ç—Ç–æ, –∫–æ–Ω–µ—á–Ω–æ, –≥—Ä–æ–º–æ–∑–¥–∫–æ –∏ —à–∞—Ç–∫–æ-–≤–∞–ª–∫–æ. –ò –Ω–µ —Ä–∞–±–æ—Ç–∞–µ—Ç, –ø–æ–∫–∞ –∫–æ–Ω–¥–µ–Ω—Å–∞—Ç–æ—Ä—ã –Ω–µ —Ä–∞–∑—Ä—è–¥—è—Ç—Å—è –ø–æ—Å–ª–µ –æ—Ç–∫–ª—é—á–µ–Ω–∏—è –ø–∏—Ç–∞–Ω–∏—è. –ù–æ —Ç–µ–º –Ω–µ –º–µ–Ω–µ–µ... –í–ª–æ–∂–µ–Ω–∏–µ:

DS1Z_QuickPrint1.png [46.07 KiB]

–°–∫–∞—á–∏–≤–∞–Ω–∏–π: 533

DS1Z_QuickPrint1.png [46.07 KiB]

–°–∫–∞—á–∏–≤–∞–Ω–∏–π: 533

--- –ü–æ—Å–ª–µ –ø–µ—Ä–≤–æ–≥–æ —Ç–∞–∫—Ç–∞ –¥–æ–ª–∂–Ω–∞ –ø–æ—è–≤–∏—Ç—Å—è 1. –•–º... –ó–∞–º—ã—Å–µ–ª –ø–æ–Ω—è–ª. –ù–∞–¥–æ –ø–æ–ø—Ä–æ–±–æ–≤–∞—Ç—å! ... –Ý–∞–±–æ—Ç–∞–µ—Ç –æ—Ç–ª–∏—á–Ω–æ! –° —Ç–µ–º —Ç–æ–ª—å–∫–æ –Ω–µ–∑–Ω–∞—á–∏—Ç–µ–ª—å–Ω—ã–º –∑–∞–º–µ—á–∞–Ω–∏–µ–º, —á—Ç–æ –∫–∞–∂–¥—ã–π —Ü–∏–∫–ª "–ø–æ 8" –æ–Ω–∞ –ø—Ä–æ–ø—É—Å–∫–∞–µ—Ç –æ–¥–∏–Ω —Ç–∞–∫—Ç: –ø—Ä–æ–≤–æ–¥–∏—Ç –µ–≥–æ –≤ –ø–æ–ª–Ω–æ—Å—Ç—å—é –≤—ã–∫–ª—é—á–µ–Ω–Ω–æ–º —Å–æ—Å—Ç–æ—è–Ω–∏–∏. –¢–æ –µ—Å—Ç—å –µ—Å–ª–∏ —á–∞—Å—Ç–æ—Ç–∞ —Ç–∞–∫—Ç–æ–≤–æ–≥–æ –≥–µ–Ω–µ—Ä–∞—Ç–æ—Ä–∞ —Ä–∞–≤–Ω–∞ 72–ì—Ü, —Ç–æ –∫–∞–∂–¥—ã–π –¥–∏–æ–¥ –±—É–¥–µ—Ç –º–µ—Ä—Ü–∞—Ç—å —Å —á–∞—Å—Ç–æ—Ç–æ–π 8 –ì—Ü, –∞ –Ω–µ 9 –ì—Ü. –û–¥–Ω–∞–∫–æ –µ—Å–ª–∏ –Ω–∞ D –∑–∞–≤–µ—Å—Ç–∏ –¥–∞–Ω–Ω—ã–µ –∫–∞–∫ —Å –∏–Ω–≤–µ—Ä—Ç–µ—Ä–∞, —Ç–∞–∫ –∏ —Å RQ7 —á–µ—Ä–µ–∑ –¥–∏–æ–¥—ã (–¥–æ–±–∞–≤–∏–≤ –Ω–∞ D pull-down —Ä–µ–∑–∏—Å—Ç–æ—Ä), —Ç–æ —ç—Ñ—Ñ–µ–∫—Ç –ø—Ä–æ–ø—É—â–µ–Ω–Ω–æ–≥–æ —Ç–∞–∫—Ç–∞ –∏—Å—á–µ–∑–Ω–µ—Ç.

–ü–æ—Å–ª–µ–¥–Ω–∏–π —Ä–∞–∑ —Ä–µ–¥–∞–∫—Ç–∏—Ä–æ–≤–∞–ª–æ—Å—å KorbenDallas –ü—Ç —Ñ–µ–≤ 12, 2021 23:31:24, –≤—Å–µ–≥–æ —Ä–µ–¥–∞–∫—Ç–∏—Ä–æ–≤–∞–ª–æ—Å—å 3 —Ä–∞–∑(–∞).

|

|

| –í–µ—Ä–Ω—É—Ç—å—Å—è –Ω–∞–≤–µ—Ä—Ö |

|

|

diplodok

|

–ó–∞–≥–æ–ª–æ–≤–æ–∫ —Å–æ–æ–±—â–µ–Ω–∏—è: Re: –ò–Ω–∏—Ü–∏–∞–ª–∏–∑–∏—Ä–æ–≤–∞—Ç—å —Ä–µ–≥–∏—Å—Ç—Ä 74HC595N  –î–æ–±–∞–≤–ª–µ–Ω–æ: –î–æ–±–∞–≤–ª–µ–Ω–æ: –ü—Ç —Ñ–µ–≤ 12, 2021 14:41:55 |

|

| –ì–æ–≤–æ—Ä—è—â–∏–π —Å —Ç–µ–∫—Å—Ç–æ–ª–∏—Ç–æ–º |

–ö–∞—Ä–º–∞: 20

–Ý–µ–π—Ç–∏–Ω–≥ —Å–æ–æ–±—â–µ–Ω–∏–π: 513

–ó–∞—Ä–µ–≥–∏—Å—Ç—Ä–∏—Ä–æ–≤–∞–Ω: –ß—Ç –∞–≤–≥ 10, 2017 20:57:51

–°–æ–æ–±—â–µ–Ω–∏–π: 1692

–Ý–µ–π—Ç–∏–Ω–≥ —Å–æ–æ–±—â–µ–Ω–∏—è: 0

|

KorbenDallas –ø–∏—Å–∞–ª(–∞): –ø–æ–ª–Ω–æ—Å—Ç—å—é –≤—ã–∫–ª—é—á–µ–Ω–Ω–æ–º —Å–æ—Å—Ç–æ—è–Ω–∏–∏. –°—Ç—Ä–∞–Ω–Ω–æ. Z —Å–æ—Å—Ç–æ—è–Ω–∏–µ –¥–æ–ª–∂–Ω–æ –ø–æ–ª—É—á–∞—Ç—å—Å—è —Ç–æ–ª—å–∫–æ –ø—Ä–∏ –ø–æ–¥–∞—á–µ 1 –Ω–∞ –≤—Ö. –û–ï. ???? –ù–æ –í—ã –Ω–∞—à–ª–∏ —Ä–µ—à–µ–Ω–∏–µ. –ü–æ–∑–¥—Ä–∞–≤–ª—è—é. –Ø —Å—Ö–µ–º—É –Ω–µ –¥–µ–ª–∞–ª, –Ω–æ –∑–¥–µ—Å—å –º–æ–∂–Ω–æ –ø–æ–ª—É—á–∞—Ç—å –∏ –¥—Ä—É–≥–∏–µ "–∑–∞–ø–æ–ª–Ω–µ–Ω–∏—è" —Ä–µ–≥–∏—Å—Ç—Ä–∞. –¢–æ–ª—å–∫–æ –≤—Ä–µ–º—è "—É—Å—Ç–∞–Ω–æ–≤–∫–∏" –Ω–µ –±—É–¥–µ—Ç 1 —Ç–∞–∫—Ç. –∞ –±–æ–ª—å—à–µ

|

|

| –í–µ—Ä–Ω—É—Ç—å—Å—è –Ω–∞–≤–µ—Ä—Ö |

|

|

KorbenDallas

|

–ó–∞–≥–æ–ª–æ–≤–æ–∫ —Å–æ–æ–±—â–µ–Ω–∏—è: Re: –ò–Ω–∏—Ü–∏–∞–ª–∏–∑–∏—Ä–æ–≤–∞—Ç—å —Ä–µ–≥–∏—Å—Ç—Ä 74HC595N  –î–æ–±–∞–≤–ª–µ–Ω–æ: –î–æ–±–∞–≤–ª–µ–Ω–æ: –ü—Ç —Ñ–µ–≤ 12, 2021 19:53:26 |

|

| –í—Å—Ç–∞–ª –Ω–∞ –ª–∞–ø—ã |

|

–ö–∞—Ä–º–∞: 1

–Ý–µ–π—Ç–∏–Ω–≥ —Å–æ–æ–±—â–µ–Ω–∏–π: -1

–ó–∞—Ä–µ–≥–∏—Å—Ç—Ä–∏—Ä–æ–≤–∞–Ω: –ü–Ω –æ–∫—Ç 31, 2016 06:23:19

–°–æ–æ–±—â–µ–Ω–∏–π: 93

–Ý–µ–π—Ç–∏–Ω–≥ —Å–æ–æ–±—â–µ–Ω–∏—è: 0

|

KorbenDallas –ø–∏—Å–∞–ª(–∞): –ø–æ–ª–Ω–æ—Å—Ç—å—é –≤—ã–∫–ª—é—á–µ–Ω–Ω–æ–º —Å–æ—Å—Ç–æ—è–Ω–∏–∏. –°—Ç—Ä–∞–Ω–Ω–æ. Z —Å–æ—Å—Ç–æ—è–Ω–∏–µ –¥–æ–ª–∂–Ω–æ –ø–æ–ª—É—á–∞—Ç—å—Å—è —Ç–æ–ª—å–∫–æ –ø—Ä–∏ –ø–æ–¥–∞—á–µ 1 –Ω–∞ –≤—Ö. –û–ï. ???? –ê –ø—Ä–∏ —á–µ–º –∑–¥–µ—Å—å Z —Å–æ—Å—Ç–æ—è–Ω–∏–µ? –í–∞—à–∞ —Å—Ö–µ–º–∞ –∏–∑–Ω–∞—á–∞–ª—å–Ω–æ –Ω–µ –∏—Å–ø–æ–ª—å–∑—É–µ—Ç –≤—ã—Ö–æ–¥ –ø–µ—Ä–µ–Ω–æ—Å–∞ RQ7. –í–º–µ—Å—Ç–æ —ç—Ç–æ–≥–æ –æ–Ω–∞ –∂–¥–µ—Ç, –ø–æ–∫–∞ –≤—Å–µ –≤—ã—Ö–æ–¥—ã –ø–æ–≥–∞—Å–Ω—É—Ç, –∏ –≤ –æ—Ç–≤–µ—Ç —Å–Ω–æ–≤–∞ –≥–µ–Ω–µ—Ä–∏—Ä—É–µ—Ç –µ–¥–∏–Ω–∏—Ü—É –Ω–∞ –≤—Ö–æ–¥–µ D. –ò–º–µ–Ω–Ω–æ —ç—Ç–æ –∏ —Ç—Ä–µ–±—É–µ—Ç –æ–¥–∏–Ω —Ç–∞–∫—Ç "—Ç–µ–º–Ω–æ—Ç—ã" –Ω–∞ –≤—Å–µ—Ö –≤—Ö–æ–¥–∞—Ö –≤ –∫–æ–Ω—Ü–µ –∫–∞–∂–¥–æ–≥–æ "–ø—Ä–æ–±–µ–≥–∞". –¢–æ –µ—Å—Ç—å, –æ–±—Ä–∞–∑–Ω–æ –≤—ã—Ä–∞–∂–∞—è—Å—å, –≤–∞—à–∞ —Å—Ö–µ–º–∞ –Ω–µ –≥–æ–Ω—è–µ—Ç –æ–¥–Ω—É –∏ —Ç—É –∂–µ –µ–¥–∏–Ω–∏—Ü—É –ø–æ –∫—Ä—É–≥—É, –∞ –ø—Ä–æ–≥–æ–Ω—è–µ—Ç –µ–¥–∏–Ω–∏—Ü—É —á–µ—Ä–µ–∑ –≤—Å–µ —Ä–∞–∑—Ä—è–¥—ã, –∞ –∑–∞—Ç–µ–º "—Ä–æ–∂–∞–µ—Ç" —Å–æ–≤–µ—Ä—à–µ–Ω–Ω–æ –Ω–æ–≤—É—é –µ–¥–∏–Ω–∏—Ü—É –Ω–∞ –≤—Ö–æ–¥–µ D —Å –¥—Ä—É–≥–æ–π —Å—Ç–æ—Ä–æ–Ω—ã  –ï—Å–ª–∏ –∂–µ –∞–∫–∫—É—Ä–∞—Ç–Ω–æ –∑–∞—Ü–∏–∫–ª–∏—Ç—å RQ7 –Ω–∞ D, —Ç–æ —Ç–æ–≥–¥–∞ –µ–¥–∏–Ω–∏—Ü—É –≤–∞—à –∏–Ω–≤–µ—Ä—Ç–µ—Ä –±—É–¥–µ—Ç –≥–µ–Ω–µ—Ä–∏—Ä–æ–≤–∞—Ç—å —Ç–æ–ª—å–∫–æ –æ–¥–∏–Ω —Ä–∞–∑: –Ω–∞ —ç—Ç–∞–ø–µ –∏–Ω–∏—Ü–∏–∞–ª–∏–∑–∞—Ü–∏–∏. –ê –¥–∞–ª–µ–µ —É–∂–µ –æ–Ω–∞ —Å–∞–º–∞ –±—É–¥–µ—Ç –≤–µ—á–Ω–æ –±–µ–≥–∞—Ç—å –ø–æ –∫—Ä—É–≥—É, –±–µ–∑ —ç—Ç–∞–ø–∞ "—Ç–µ–º–Ω–æ—Ç—ã".

|

|

| –í–µ—Ä–Ω—É—Ç—å—Å—è –Ω–∞–≤–µ—Ä—Ö |

|

|

|

–Ý–µ–∫–ª–∞–º–∞

|

|

|

|

|

|

|

|

|

diplodok

|

–ó–∞–≥–æ–ª–æ–≤–æ–∫ —Å–æ–æ–±—â–µ–Ω–∏—è: Re: –ò–Ω–∏—Ü–∏–∞–ª–∏–∑–∏—Ä–æ–≤–∞—Ç—å —Ä–µ–≥–∏—Å—Ç—Ä 74HC595N  –î–æ–±–∞–≤–ª–µ–Ω–æ: –î–æ–±–∞–≤–ª–µ–Ω–æ: –ü—Ç —Ñ–µ–≤ 12, 2021 20:58:28 |

|

| –ì–æ–≤–æ—Ä—è—â–∏–π —Å —Ç–µ–∫—Å—Ç–æ–ª–∏—Ç–æ–º |

–ö–∞—Ä–º–∞: 20

–Ý–µ–π—Ç–∏–Ω–≥ —Å–æ–æ–±—â–µ–Ω–∏–π: 513

–ó–∞—Ä–µ–≥–∏—Å—Ç—Ä–∏—Ä–æ–≤–∞–Ω: –ß—Ç –∞–≤–≥ 10, 2017 20:57:51

–°–æ–æ–±—â–µ–Ω–∏–π: 1692

–Ý–µ–π—Ç–∏–Ω–≥ —Å–æ–æ–±—â–µ–Ω–∏—è: 0

|

|

–ü–æ–ª–Ω–æ—Å—Ç—å—é –≤—ã–∫–ª—é—á–µ–Ω–Ω–æ–µ —Å–æ—Å—Ç–æ—è–Ω–∏–µ - —ç—Ç–æ –∏ –µ—Å—Ç—å Z

–°–∫–æ–ª—å–∫–æ –¥–∏–æ–¥–∞ –í—ã —Å–æ–µ–¥–∏–Ω–∏–ª–∏ –∫ –≤—ã—Ö–æ–¥–∞–º–∏ 7 –∏–ª–∏ 8?

–õ–æ–≥–∏–∫–∞ —Ç–∞–∫–∞—è - –µ—Å–ª–∏ –Ω–∞ –∫–∞–∫–æ–º-—Ç–æ –≤—ã—Ö–æ–¥–µ (Q0-Q6) –µ—Å—Ç—å 1 —Ç–æ –Ω–∞ –≤—Ö–æ–¥–µ D –ø—Ä–∏—Å—É—Å—Ç–≤—É–µ—Ç 0

–ï—Å–ª–∏ –Ω–∞ –≤—Å–µ —Å Q0 –¥–æ Q6 –µ—Å—Ç—å 0 —Ç–æ –Ω–∞ –≤—Ö–æ–¥–µ –î - 1.

M—ã –≤—ã—Ö–æ–¥ Q7 –Ω–µ –æ–±—Ö–≤–∞—Ç—ã–≤–∞–µ–º —Ü–µ–ø—å—é –û–°

–î–∞ –ª–∞–¥–Ω–æ. –í–∞–∂–Ω–æ, —á—Ç–æ —Å—Ö–µ–º–∞ —Ä–∞–±–æ—Ç–∞–µ—Ç.

|

|

| –í–µ—Ä–Ω—É—Ç—å—Å—è –Ω–∞–≤–µ—Ä—Ö |

|

|

KorbenDallas

|

–ó–∞–≥–æ–ª–æ–≤–æ–∫ —Å–æ–æ–±—â–µ–Ω–∏—è: Re: –ò–Ω–∏—Ü–∏–∞–ª–∏–∑–∏—Ä–æ–≤–∞—Ç—å —Ä–µ–≥–∏—Å—Ç—Ä 74HC595N  –î–æ–±–∞–≤–ª–µ–Ω–æ: –î–æ–±–∞–≤–ª–µ–Ω–æ: –ü—Ç —Ñ–µ–≤ 12, 2021 21:22:30 |

|

| –í—Å—Ç–∞–ª –Ω–∞ –ª–∞–ø—ã |

|

–ö–∞—Ä–º–∞: 1

–Ý–µ–π—Ç–∏–Ω–≥ —Å–æ–æ–±—â–µ–Ω–∏–π: -1

–ó–∞—Ä–µ–≥–∏—Å—Ç—Ä–∏—Ä–æ–≤–∞–Ω: –ü–Ω –æ–∫—Ç 31, 2016 06:23:19

–°–æ–æ–±—â–µ–Ω–∏–π: 93

–Ý–µ–π—Ç–∏–Ω–≥ —Å–æ–æ–±—â–µ–Ω–∏—è: 0

|

–°–∫–æ–ª—å–∫–æ –¥–∏–æ–¥–∞ –í—ã —Å–æ–µ–¥–∏–Ω–∏–ª–∏ –∫ –≤—ã—Ö–æ–¥–∞–º–∏ 7 –∏–ª–∏ 8?

–õ–æ–≥–∏–∫–∞ —Ç–∞–∫–∞—è - –µ—Å–ª–∏ –Ω–∞ –∫–∞–∫–æ–º-—Ç–æ –≤—ã—Ö–æ–¥–µ (Q0-Q6) –µ—Å—Ç—å 1 —Ç–æ –Ω–∞ –≤—Ö–æ–¥–µ D –ø—Ä–∏—Å—É—Å—Ç–≤—É–µ—Ç 0

–ï—Å–ª–∏ –Ω–∞ –≤—Å–µ —Å Q0 –¥–æ Q6 –µ—Å—Ç—å 0 —Ç–æ –Ω–∞ –≤—Ö–æ–¥–µ –î - 1.

M—ã –≤—ã—Ö–æ–¥ Q7 –Ω–µ –æ–±—Ö–≤–∞—Ç—ã–≤–∞–µ–º —Ü–µ–ø—å—é –û–° –ê, –≤–æ—Ç –æ–Ω–æ —á—Ç–æ! –≠—Ç–æ—Ç –º–æ–º–µ–Ω—Ç —è –Ω–µ —Ä–∞–∑–≥–ª—è–¥–µ–ª –≤ –≤–∞—à–µ–π —Å—Ö–µ–º–µ. –î–∞, –∫–æ–Ω–µ—á–Ω–æ, –µ—Å–ª–∏ Q7 –∏—Å–∫–ª—é—á–∏—Ç—å –∏–∑ –û–°, —Ç–æ —Ñ–∞–∫—Ç–∏—á–µ—Å–∫–∏ –º—ã –ø–æ–ª—É—á–∏–º "–≥–µ–Ω–µ—Ä–∞—Ç–æ—Ä –ø–µ—Ä–µ–Ω–æ—Å–∞ –Ω–∞ –æ–¥–∏–Ω —Ç–∞–∫—Ç —Ä–∞–Ω—å—à–µ". –¢–æ–≥–¥–∞ –¥–µ–π—Å—Ç–≤–∏—Ç–µ–ª—å–Ω–æ "—Ç–µ–º–Ω—ã–π" —Ç–∞–∫—Ç –ø—Ä–æ–ø–∞–¥–µ—Ç.

|

|

| –í–µ—Ä–Ω—É—Ç—å—Å—è –Ω–∞–≤–µ—Ä—Ö |

|

|

diplodok

|

–ó–∞–≥–æ–ª–æ–≤–æ–∫ —Å–æ–æ–±—â–µ–Ω–∏—è: Re: –ò–Ω–∏—Ü–∏–∞–ª–∏–∑–∏—Ä–æ–≤–∞—Ç—å —Ä–µ–≥–∏—Å—Ç—Ä 74HC595N  –î–æ–±–∞–≤–ª–µ–Ω–æ: –î–æ–±–∞–≤–ª–µ–Ω–æ: –ü—Ç —Ñ–µ–≤ 12, 2021 21:37:08 |

|

| –ì–æ–≤–æ—Ä—è—â–∏–π —Å —Ç–µ–∫—Å—Ç–æ–ª–∏—Ç–æ–º |

–ö–∞—Ä–º–∞: 20

–Ý–µ–π—Ç–∏–Ω–≥ —Å–æ–æ–±—â–µ–Ω–∏–π: 513

–ó–∞—Ä–µ–≥–∏—Å—Ç—Ä–∏—Ä–æ–≤–∞–Ω: –ß—Ç –∞–≤–≥ 10, 2017 20:57:51

–°–æ–æ–±—â–µ–Ω–∏–π: 1692

–Ý–µ–π—Ç–∏–Ω–≥ —Å–æ–æ–±—â–µ–Ω–∏—è: 0

|

|

–ï—Å–ª–∏ –º—ã –ø–æ–¥—Å–æ–µ–¥–∏–Ω–∏–º (—Å–∫–∞–∂–µ–º) —Ç–æ–ª—å–∫–æ –¥–∏–æ–¥—ã –∫ Q0,Q1,Q2,Q3 —Ç–æ –º—ã –ø–æ–ª—É—á–∏–º –∑–∞–ø–æ–ª–Ω–µ–Ω–∏–µ 00001111

–µ—Å–ª–∏ –∫ Q0, Q2, Q4, Q6 01010101

–∏ —Ç.–¥. –∫–∞–∫ –∑–∞—Ö–æ—Ç–∏–º

–ü–ª–∞—Ç–∞ –∑–∞ —ç—Ç–æ - –≤—Ä–µ–º—è "—É—Å—Ç–∞–Ω–æ–≤–∫–∏" –ø–µ—Ä–≤–æ–≥–æ –Ω–∞–±–æ—Ä–∞ - –¥–æ 8 —Ç–∞–∫—Ç–∞

|

|

| –í–µ—Ä–Ω—É—Ç—å—Å—è –Ω–∞–≤–µ—Ä—Ö |

|

|

KorbenDallas

|

–ó–∞–≥–æ–ª–æ–≤–æ–∫ —Å–æ–æ–±—â–µ–Ω–∏—è: Re: –ò–Ω–∏—Ü–∏–∞–ª–∏–∑–∏—Ä–æ–≤–∞—Ç—å —Ä–µ–≥–∏—Å—Ç—Ä 74HC595N  –î–æ–±–∞–≤–ª–µ–Ω–æ: –î–æ–±–∞–≤–ª–µ–Ω–æ: –ü—Ç —Ñ–µ–≤ 12, 2021 23:50:58 |

|

| –í—Å—Ç–∞–ª –Ω–∞ –ª–∞–ø—ã |

|

–ö–∞—Ä–º–∞: 1

–Ý–µ–π—Ç–∏–Ω–≥ —Å–æ–æ–±—â–µ–Ω–∏–π: -1

–ó–∞—Ä–µ–≥–∏—Å—Ç—Ä–∏—Ä–æ–≤–∞–Ω: –ü–Ω –æ–∫—Ç 31, 2016 06:23:19

–°–æ–æ–±—â–µ–Ω–∏–π: 93

–Ý–µ–π—Ç–∏–Ω–≥ —Å–æ–æ–±—â–µ–Ω–∏—è: 0

|

–ü–æ–ª–Ω–æ—Å—Ç—å—é –≤—ã–∫–ª—é—á–µ–Ω–Ω–æ–µ —Å–æ—Å—Ç–æ—è–Ω–∏–µ - —ç—Ç–æ –∏ –µ—Å—Ç—å Z –Ø, –≤–∏–¥–∏–º–æ, –Ω–µ–ø—Ä–∞–≤–∏–ª—å–Ω–æ –≤—ã—Ä–∞–∑–∏–ª—Å—è —Ç–µ—Ä–º–∏–Ω–æ–ª–æ–≥–∏—á–µ—Å–∫–∏. –ü–æ–¥ "–ø–æ–ª–Ω–æ—Å—Ç—å—é –≤—ã–∫–ª—é—á–µ–Ω–Ω—ã–º —Å–æ—Å—Ç–æ—è–Ω–∏–µ–º" —è –∏–º–µ–ª –≤ –≤–∏–¥—É —Å–æ—Å—Ç–æ—è–Ω–∏–µ Q0=Q1=...=Q7=0, —Ç–æ –µ—Å—Ç—å –ª–æ–≥–∏—á–µ—Å–∫–∏–µ –Ω—É–ª–∏ –Ω–∞ –≤—Å–µ—Ö Q-–≤—ã—Ö–æ–¥–∞—Ö, –∞ –Ω–µ —Å–æ—Å—Ç–æ—è–Ω–∏–µ hi-Z –Ω–∞ –≤—Å–µ—Ö –≤—ã—Ö–æ–¥–∞—Ö. –ö–æ–Ω–µ—á–Ω–æ, —Å–æ—Å—Ç–æ—è–Ω–∏–µ hi-Z –º–æ–∂–Ω–æ –ø–æ–ª—É—á–∏—Ç—å —Ç–æ–ª—å–∫–æ –µ–¥–∏–Ω–∏—Ü–µ–π –Ω–∞ OE, –Ω–æ —è –≤–µ–ª —Ä–µ—á—å –Ω–µ –æ–± —ç—Ç–æ–º.

|

|

| –í–µ—Ä–Ω—É—Ç—å—Å—è –Ω–∞–≤–µ—Ä—Ö |

|

|

BOB51

|

–ó–∞–≥–æ–ª–æ–≤–æ–∫ —Å–æ–æ–±—â–µ–Ω–∏—è: Re: –ò–Ω–∏—Ü–∏–∞–ª–∏–∑–∏—Ä–æ–≤–∞—Ç—å —Ä–µ–≥–∏—Å—Ç—Ä 74HC595N  –î–æ–±–∞–≤–ª–µ–Ω–æ: –î–æ–±–∞–≤–ª–µ–Ω–æ: –°–± —Ñ–µ–≤ 13, 2021 12:20:52 |

|

| –î—Ä—É–≥ –ö–æ—Ç–∞ |

|

–ö–∞—Ä–º–∞: 96

–Ý–µ–π—Ç–∏–Ω–≥ —Å–æ–æ–±—â–µ–Ω–∏–π: 1502

–ó–∞—Ä–µ–≥–∏—Å—Ç—Ä–∏—Ä–æ–≤–∞–Ω: –í—Ç –º–∞—Ä 16, 2010 22:02:27

–°–æ–æ–±—â–µ–Ω–∏–π: 15453

–û—Ç–∫—É–¥–∞: –î–û–ù–ï–¶–ö

–Ý–µ–π—Ç–∏–Ω–≥ —Å–æ–æ–±—â–µ–Ω–∏—è: 0

|

–£ 595 –Ω–µ—Ç –≤—ã–≤–æ–¥–∞ –æ–±–Ω—É–ª–µ–Ω–∏—è —Å–æ–¥–µ—Ä–∂–∏–º–æ–≥–æ (–Ω–∏ –¥–ª—è –Ω–∞–∫–æ–ø–∏—Ç–µ–ª—å–Ω–æ–π —á–∞—Å—Ç–∏ –Ω–∏ –¥–ª—è —Å–¥–≤–∏–≥–æ–≤–æ–≥–æ —Ä–µ–≥–∏—Å—Ç—Ä–∞). –¢–∞–º –µ–¥–∏–Ω—Å—Ç–≤–µ–Ω–Ω–æ –≤–æ–∑–º–æ–∂–Ω–æ–µ —Ä–µ—à–µ–Ω–∏–µ Z-—Å–æ—Å—Ç–æ—è–Ω–∏–µ –¥–æ –ø–µ—Ä–≤–æ–π –∑–∞–≥—Ä—É–∑–∫–∏ –ø–æ—Å–ª–µ–¥–æ–≤–∞—Ç–µ–ª—å–Ω–æ–≥–æ —Ä–µ–≥–∏—Å—Ç—Ä–∞ –∏ –ø–æ—Å–ª–µ–¥—É—é—â–µ–π –ø–µ—Ä–µ–∑–∞–ø–∏—Å–∏ —Å–æ–¥–µ—Ä–∂–∏–º–æ–≥–æ –≤ –ø–∞—Ä–∞–ª–ª–µ–ª—å–Ω—ã–π. –ê —ç—Ç–æ —É–∂–µ –Ω–∞ –ø—Ä–æ—Å—Ç–æ–π –ª–æ–≥–∏–∫–µ –¥–µ–ª–∞—Ç—å —Å–ª–æ–∂–Ω–æ - –Ω–∞–¥–æ –¥–∞—Ç—å —Å–µ—Ä–∏—é —Ç–∞–∫—Ç–æ–≤—ã—Ö –∏–º–ø—É–ª—å—Å–æ–≤ –ø—Ä–∏ 0 –Ω–∞ –≤—Ö–æ–¥–µ, –∑–∞—Ç–µ–º –æ–¥–∏–Ω –¥–ª—è –ø–µ—Ä–µ–∑–∞–ø–∏—Å–∏ —Å–æ–¥–µ—Ä–∂–∏–º–æ–≥–æ. –≠—Ç–æ —É–∂–µ —Å—á–µ—Ç—á–∏–∫–∏, –¥–µ—à–∏—Ñ—Ä–∞—Ç–æ—Ä—ã, —Å—Ö–µ–º—ã —Å–æ–≤–ø–∞–¥–µ–Ω–∏—è, –¥–æ–ø–æ–ª–Ω–∏—Ç–µ–ª—å–Ω–∞—è —à–∏–Ω–∞ –Ω–∞—á–∞–ª—å–Ω–æ–≥–æ —Å–±—Ä–æ—Å–∞ –ø—Ä–∏ –ø–æ–¥–∞—á–µ –ø–∏—Ç–∞–Ω–∏—è. –í–æ–±—â–µ–º - —Å–¥–µ–ª–∞—Ç—å –º–æ–∂–Ω–æ... –æ—Å–æ–±–æ –≤ —É—á–µ–±–Ω—ã—Ö —Ü–µ–ª—è—Ö —Ö–æ—Ä–æ—à–∞—è –ø—Ä–∞–∫—Ç–∏–∫–∞. –û–¥–Ω–∞–∫–æ –≥–æ—Ä–æ–¥—É—à–∫–∞ –º–∏–Ω–∏–º—É–º –≤ –¥–µ—Å—è—Ç–æ–∫ –∫–æ—Ä–ø—É—Å–æ–≤ –±—É–¥–µ—Ç.

|

|

| –í–µ—Ä–Ω—É—Ç—å—Å—è –Ω–∞–≤–µ—Ä—Ö |

|

|

diplodok

|

–ó–∞–≥–æ–ª–æ–≤–æ–∫ —Å–æ–æ–±—â–µ–Ω–∏—è: Re: –ò–Ω–∏—Ü–∏–∞–ª–∏–∑–∏—Ä–æ–≤–∞—Ç—å —Ä–µ–≥–∏—Å—Ç—Ä 74HC595N  –î–æ–±–∞–≤–ª–µ–Ω–æ: –î–æ–±–∞–≤–ª–µ–Ω–æ: –°–± —Ñ–µ–≤ 13, 2021 14:00:05 |

|

| –ì–æ–≤–æ—Ä—è—â–∏–π —Å —Ç–µ–∫—Å—Ç–æ–ª–∏—Ç–æ–º |

–ö–∞—Ä–º–∞: 20

–Ý–µ–π—Ç–∏–Ω–≥ —Å–æ–æ–±—â–µ–Ω–∏–π: 513

–ó–∞—Ä–µ–≥–∏—Å—Ç—Ä–∏—Ä–æ–≤–∞–Ω: –ß—Ç –∞–≤–≥ 10, 2017 20:57:51

–°–æ–æ–±—â–µ–Ω–∏–π: 1692

–Ý–µ–π—Ç–∏–Ω–≥ —Å–æ–æ–±—â–µ–Ω–∏—è: 0

|

BOB51 –ø–∏—Å–∞–ª(–∞): –£ 595 –Ω–µ—Ç –≤—ã–≤–æ–¥–∞ –æ–±–Ω—É–ª–µ–Ω–∏—è —Å–æ–¥–µ—Ä–∂–∏–º–æ–≥–æ (–Ω–∏ –¥–ª—è –Ω–∞–∫–æ–ø–∏—Ç–µ–ª—å–Ω–æ–π —á–∞—Å—Ç–∏ –Ω–∏ –¥–ª—è —Å–¥–≤–∏–≥–æ–≤–æ–≥–æ —Ä–µ–≥–∏—Å—Ç—Ä–∞). –ì–∞–¥—ã! –ò –∫–æ–≥–¥–∞ —É—Å–ø–µ–ª–∏ —É–±—Ä–∞—Ç—å –æ–±–Ω—É–ª–µ–Ω–∏–µ —Å–¥–≤–∏–≥. —Ä–µ–≥–∏—Å—Ç—Ä–∞? BOB51 –ø–∏—Å–∞–ª(–∞): –¢–∞–º –µ–¥–∏–Ω—Å—Ç–≤–µ–Ω–Ω–æ –≤–æ–∑–º–æ–∂–Ω–æ–µ —Ä–µ—à–µ–Ω–∏–µ Z-—Å–æ—Å—Ç–æ—è–Ω–∏–µ –¥–æ –ø–µ—Ä–≤–æ–π –∑–∞–≥—Ä—É–∑–∫–∏ –ø–æ—Å–ª–µ–¥–æ–≤–∞—Ç–µ–ª—å–Ω–æ–≥–æ —Ä–µ–≥–∏—Å—Ç—Ä–∞ –∏ –ø–æ—Å–ª–µ–¥—É—é—â–µ–π –ø–µ—Ä–µ–∑–∞–ø–∏—Å–∏ —Å–æ–¥–µ—Ä–∂–∏–º–æ–≥–æ –≤ –ø–∞—Ä–∞–ª–ª–µ–ª—å–Ω—ã–π. –í—ã –æ —á–µ–º? BOB51 –ø–∏—Å–∞–ª(–∞): –û–¥–Ω–∞–∫–æ –≥–æ—Ä–æ–¥—É—à–∫–∞ –º–∏–Ω–∏–º—É–º –≤ –¥–µ—Å—è—Ç–æ–∫ –∫–æ—Ä–ø—É—Å–æ–≤ –±—É–¥–µ—Ç. –ü—Ä–æ—á–∏—Ç–∞–π—Ç–µ —á—Ç–æ —Ç—Ä–µ–±–æ–≤–∞–ª –¢–° –∏ –ø–æ—Å–º–æ—Ç—Ä–∏—Ç–µ –Ω–∞ —Å—Ö–µ–º—É. KorbenDallas –ø–∏—Å–∞–ª(–∞): –Ω–µ–ø—Ä–∞–≤–∏–ª—å–Ω–æ –≤—ã—Ä–∞–∑–∏–ª—Å—è —Ç–µ—Ä–º–∏–Ω–æ–ª–æ–≥–∏—á–µ—Å–∫–∏. –î–ª—è –≤—ã—Ö–æ–¥–∞ —Å Z state –µ—Å—Ç—å —Ç—Ä–∏ —Å–æ—Å—Ç–æ—è–Ω–∏—è 0 - Lo 1 - Hi Z - –≤—ã–∫–ª—é—á. –Ø –ø–æ–Ω—è–ª –æ —á–µ–º –í—ã, –Ω–æ –µ—Å–ª–∏ –í—ã —Å–∫–∞–∂–µ—Ç–µ —Ç–∞–∫ –ø—Ä–µ–ø–æ–¥–∞ –æ–Ω (–∫–∞–∫ —è) —Å—Ç–∞–Ω–µ—Ç –ø—Ä–∏–¥–∏—Ä–∞—Ç—å—Å—è.

|

|

| –í–µ—Ä–Ω—É—Ç—å—Å—è –Ω–∞–≤–µ—Ä—Ö |

|

|

KorbenDallas

|

–ó–∞–≥–æ–ª–æ–≤–æ–∫ —Å–æ–æ–±—â–µ–Ω–∏—è: Re: –ò–Ω–∏—Ü–∏–∞–ª–∏–∑–∏—Ä–æ–≤–∞—Ç—å —Ä–µ–≥–∏—Å—Ç—Ä 74HC595N  –î–æ–±–∞–≤–ª–µ–Ω–æ: –î–æ–±–∞–≤–ª–µ–Ω–æ: –í—Å —Ñ–µ–≤ 14, 2021 11:27:06 |

|

| –í—Å—Ç–∞–ª –Ω–∞ –ª–∞–ø—ã |

|

–ö–∞—Ä–º–∞: 1

–Ý–µ–π—Ç–∏–Ω–≥ —Å–æ–æ–±—â–µ–Ω–∏–π: -1

–ó–∞—Ä–µ–≥–∏—Å—Ç—Ä–∏—Ä–æ–≤–∞–Ω: –ü–Ω –æ–∫—Ç 31, 2016 06:23:19

–°–æ–æ–±—â–µ–Ω–∏–π: 93

–Ý–µ–π—Ç–∏–Ω–≥ —Å–æ–æ–±—â–µ–Ω–∏—è: 0

|

–í—Å–µ–º –ø—Ä–µ–∫—Ä–∞—Å–Ω–∞ —Ä–µ–∞–ª–∏–∑–∞—Ü–∏—è diplodok, –Ω–æ.. –ù–æ –≤–æ—Ç –∑–∞—Ö–æ—Ç–µ–ª–æ—Å—å –º–Ω–µ —Ç–µ–ø–µ—Ä—å, —á—Ç–æ–±—ã –≤—ã—Ö–æ–¥–Ω—ã–µ –∏–º–ø—É–ª—å—Å—ã –Ω–∞ –≤–æ—Å—å–º–∏ –≤—ã—Ö–æ–¥–∞—Ö –≤ —Å–æ–≤–æ–∫—É–ø–Ω–æ—Å—Ç–∏ –Ω–µ —Å–ª–∏–≤–∞–ª–∏—Å—å –≤ "—Å–ø–ª–æ—à–Ω–æ–π –∑–∞–±–æ—Ä", –∞ –æ—Å—Ç–∞–≤–ª—è–ª–∏ –æ—Ç–Ω–æ—Å–∏—Ç–µ–ª—å–Ω–æ –Ω–µ–±–æ–ª—å—à–∏–µ –ø—Ä–æ–º–µ–∂—É—Ç–∫–∏ –º–µ–∂–¥—É "—à—Ç–∞–∫–µ—Ç–∏–Ω–∞–º–∏". –ù–∞–¥–µ—é—Å—å, –ø–æ–Ω—è—Ç–Ω–æ, —á—Ç–æ —è –∏–º–µ—é –≤ –≤–∏–¥—É. –¢–æ –µ—Å—Ç—å –ø–æ—Å–ª–µ –∏—Å—á–µ–∑–Ω–æ–≤–µ–Ω–∏—è –ª–æ–≥–∏—á–µ—Å–∫–æ–π 1 –Ω–∞ –≤—ã—Ö–æ–¥–µ Q0 –ª–æ–≥–∏—á–µ—Å–∫–∞—è 1 –Ω–∞ –≤—ã—Ö–æ–¥–µ Q1 –¥–æ–ª–∂–Ω–∞ –ø–æ—è–≤–ª—è—Ç—å—Å—è –Ω–µ —Å—Ä–∞–∑—É, –∞ –ø–æ –ø—Ä–æ—à–µ—Å—Ç–≤–∏–∏ –∫–∞–∫–æ–≥–æ-—Ç–æ –∫–æ—Ä–æ—Ç–∫–æ–≥–æ –≤—Ä–µ–º–µ–Ω–∏. –¢–æ –µ—Å—Ç—å, —Å–∫–∞–∂–µ–º, 90% –≤—Ä–µ–º–µ–Ω–∏ –Ω–∞ –æ–¥–Ω–æ–º –∏–∑ –≤—ã—Ö–æ–¥–æ–≤ –ø—Ä–∏—Å—É—Ç—Å—Ç–≤—É–µ—Ç –ª–æ–≥–∏—á–µ—Å–∫–∞—è 1, –∞ 10% –≤—Ä–µ–º–µ–Ω–∏ –≤—Å–µ –≤—ã—Ö–æ–¥—ã —Ä–∞–≤–Ω—ã 0. –¢—É—Ç –∑–∞–º–∞–Ω—á–∏–≤–æ –±—ã–ª–æ –±—ã –∏—Å–ø–æ–ª—å–∑–æ–≤–∞—Ç—å –≤—Ö–æ–¥ OE, –æ—Ç —Ç–æ–≥–æ –∂–µ —Ç–∞–∫—Ç–æ–≤–æ–≥–æ –≥–µ–Ω–µ—Ä–∞—Ç–æ—Ä–∞, –∫–æ—Ç–æ—Ä—ã–π –¥–≤–∏–∂–µ—Ç –Ω–∞—à —Ä–µ–≥–∏—Å—Ç—Ä. –°–¥–µ–ª–∞—Ç—å –∫–æ—ç—Ñ—Ñ–∏—Ü–∏–µ–Ω—Ç –∑–∞–ø–æ–ª–Ω–µ–Ω–∏—è –Ω–∞ —Ç–∞–∫—Ç–æ–≤–æ–º –≥–µ–Ω–µ—Ä–∞—Ç–æ—Ä–µ 90%, –ø–æ–ª—É—á–∏—Ç—å —Å –∏–Ω–≤–µ—Ä—Ç–µ—Ä–∞ –∫–æ—ç—Ñ—Ñ–∏—Ü–∏–µ–Ω—Ç –∑–∞–ø–æ–ª–Ω–µ–Ω–∏—è 10% –∏ –ø—É—Å—Ç–∏—Ç—å —ç—Ç–æ—Ç —Å–∏–≥–Ω–∞–ª –Ω–∞ OE. –ù–æ –≤ —Ä–µ–∞–ª–∏–∑–∞—Ü–∏–∏ diplodok —Ç–∞–∫–æ–π –Ω–æ–º–µ—Ä –Ω–µ –ø—Ä–æ–π–¥–µ—Ç –ø–æ –æ—á–µ–≤–∏–¥–Ω—ã–º –ø—Ä–∏—á–∏–Ω–∞–º: –∫–∞–∫ —Ç–æ–ª—å–∫–æ –≤—Å–µ –≤—ã—Ö–æ–¥—ã –ø–∞–¥–∞—é—Ç –≤ 0, —Å—Ä–∞–±–∞—Ç—ã–≤–∞–µ—Ç –¥–∏–æ–¥–Ω—ã–π "–¥–µ—Ç–µ–∫—Ç–æ—Ä –Ω—É–ª–µ–π" –∏ –∑–∞–ø—É—Å–∫–∞–µ—Ç –Ω–∞ –≤—Ö–æ–¥ —Ä–µ–≥–∏—Å—Ç—Ä–∞ –æ—á–µ—Ä–µ–¥–Ω—É—é –µ–¥–∏–Ω–∏—Ü—É. –ê —ç—Ç–æ –Ω–∞—Å —Å–æ–≤–µ—Ä—à–µ–Ω–Ω–æ –Ω–µ —É—Å—Ç—Ä–∞–∏–≤–∞–µ—Ç... –û—á–µ–≤–∏–¥–Ω–æ–µ –∞–ª—å—Ç–µ—Ä–Ω–∞—Ç–∏–≤–Ω–æ–µ —Ä–µ—à–µ–Ω–∏–µ: —Ä–µ–∞–ª–∏–∑–æ–≤–∞—Ç—å –≤—Å–µ –≤ —Å–∞–º—ã–π –ø–æ—Å–ª–µ–¥–Ω–∏–π –º–æ–º–µ–Ω—Ç –ø–µ—Ä–µ–¥ –≤—ã—Ö–æ–¥–æ–º, —Ç–æ –µ—Å—Ç—å –ø—Ä–æ–ø—É—Å—Ç–∏—Ç—å –≤—Å–µ –≤—ã—Ö–æ–¥—ã —á–µ—Ä–µ–∑ AND—ã –∏–ª–∏ NAND—ã, –∫–æ—Ç–æ—Ä—ã–µ –±—É–¥—É—Ç –≥–ª—É—à–∏—Ç—å –≤—Å–µ –≤—ã—Ö–æ–¥—ã –ø–æ —Å–∏–≥–Ω–∞–ª—É —Å —Ç–æ–≥–æ –∂–µ —Ç–∞–∫—Ç–æ–≤–æ–≥–æ –≥–µ–Ω–µ—Ä–∞—Ç–æ—Ä–∞. –ù–æ –¥–ª—è —ç—Ç–æ–≥–æ –ø–æ–Ω–∞–¥–æ–±—è—Ç—Å—è 8 –¥–æ–ø–æ–ª–Ω–∏—Ç–µ–ª—å–Ω—ã—Ö –ª–æ–≥–∏—á–µ—Å–∫–∏—Ö –≤–µ–Ω—Ç–∏–ª–µ–π –∏ —Ä–∞–∑–≤–æ–¥–∫–∞ –¥–ª—è –Ω–∏—Ö. –ì—Ä–æ–º–æ–∑–¥–∫–æ... –ë–æ–ª–µ–µ –æ—Å—Ç—Ä–æ—É–º–Ω—ã–π –≤–∞—Ä–∏–∞–Ω—Ç: –ø–æ—Å—ã–ª–∞–µ–º –µ–¥–∏–Ω–∏—Ü—É –Ω–∞ OE –∏ –æ–¥–Ω–æ–≤—Ä–µ–º–µ–Ω–Ω–æ –ø–æ–¥–∞–≤–ª—è–µ–º –µ–¥–∏–Ω–∏—Ü—É —Å –¥–∏–æ–¥–Ω–æ–≥–æ –¥–µ—Ç–µ–∫—Ç–æ—Ä–∞ –Ω—É–ª–µ–π... –ü–æ–Ω–∞–¥–æ–±–∏—Ç—Å—è –æ–¥–∏–Ω –¥–æ–ø–æ–ª–Ω–∏—Ç–µ–ª—å–Ω—ã–π –≤–µ–Ω—Ç–∏–ª—å... –ù–∞–¥–æ –ø–æ–ø—Ä–æ–±–æ–≤–∞—Ç—å. –¢—É—Ç, –Ω–∞–≤–µ—Ä–Ω–æ–µ, –∑–∞–ø—Ä–æ—Å—Ç–æ –º–æ–∂–Ω–æ –≤–ª–µ—Ç–µ—Ç—å –≤ –ø—Ä–æ–±–ª–µ–º—ã —Å —Ç–∞–π–º–∏–Ω–≥–æ–º. –ù–µ—Ç, –Ω–µ –ø–æ–π–¥–µ—Ç. –û–Ω–æ –≤–µ–¥—å –±—É–¥–µ—Ç –¥–∞–≤–∏—Ç—å –∏ —Ç—É –µ–¥–∏–Ω–∏—Ü—É, –∫–æ—Ç–æ—Ä–∞—è –Ω–∞–º –Ω—É–∂–Ω–∞... –£–∂–æ—Å. –î–æ–±–∞–≤–ª–µ–Ω–æ after 2 hours 10 minutes 26 seconds:–õ–æ–±–æ–≤–æ–π –≤–∞—Ä–∏–∞–Ω—Ç —Å –≤–æ—Å–µ–º—å—é –¥–æ–ø–æ–ª–Ω–∏—Ç–µ–ª—å–Ω—ã–º–∏ –≤–µ–Ω—Ç–∏–ª—è–º–∏ AND –Ω–∞ –≤—ã—Ö–æ–¥–µ –¥–∞–µ—Ç –∂–µ–ª–∞–µ–º—ã–π —Ä–µ–∑—É–ª—å—Ç–∞—Ç  –ß–µ—Ç—ã—Ä–µ —Å–æ—Å–µ–¥–Ω–∏—Ö –≤—ã—Ö–æ–¥–∞ –∏–∑ –≤–æ—Å—å–º–∏

|

|

| –í–µ—Ä–Ω—É—Ç—å—Å—è –Ω–∞–≤–µ—Ä—Ö |

|

|

diplodok

|

–ó–∞–≥–æ–ª–æ–≤–æ–∫ —Å–æ–æ–±—â–µ–Ω–∏—è: Re: –ò–Ω–∏—Ü–∏–∞–ª–∏–∑–∏—Ä–æ–≤–∞—Ç—å —Ä–µ–≥–∏—Å—Ç—Ä 74HC595N  –î–æ–±–∞–≤–ª–µ–Ω–æ: –î–æ–±–∞–≤–ª–µ–Ω–æ: –í—Å —Ñ–µ–≤ 14, 2021 13:39:55 |

|

| –ì–æ–≤–æ—Ä—è—â–∏–π —Å —Ç–µ–∫—Å—Ç–æ–ª–∏—Ç–æ–º |

–ö–∞—Ä–º–∞: 20

–Ý–µ–π—Ç–∏–Ω–≥ —Å–æ–æ–±—â–µ–Ω–∏–π: 513

–ó–∞—Ä–µ–≥–∏—Å—Ç—Ä–∏—Ä–æ–≤–∞–Ω: –ß—Ç –∞–≤–≥ 10, 2017 20:57:51

–°–æ–æ–±—â–µ–Ω–∏–π: 1692

–Ý–µ–π—Ç–∏–Ω–≥ —Å–æ–æ–±—â–µ–Ω–∏—è: 0

|

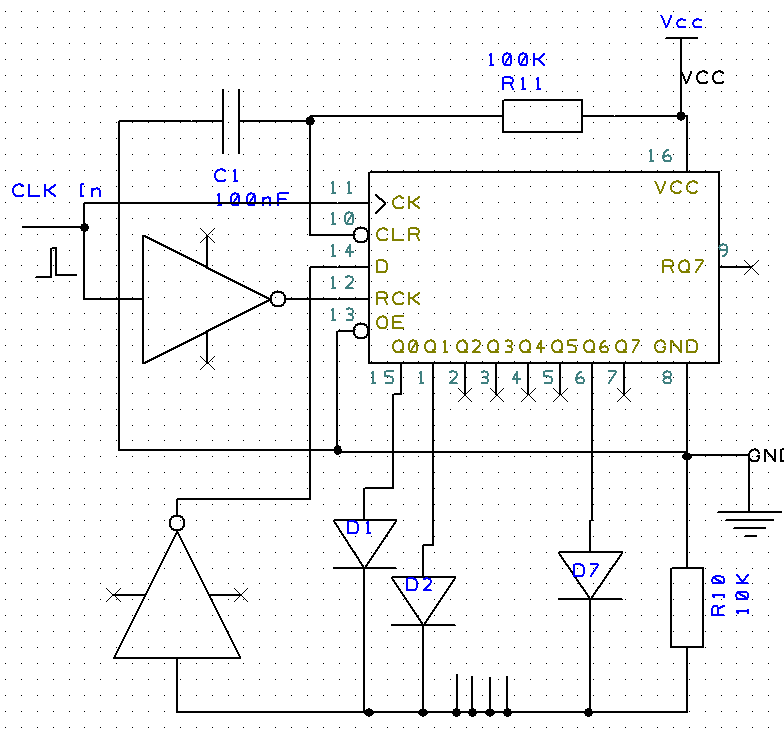

KorbenDallas –ø–∏—Å–∞–ª(–∞): –¢—É—Ç –∑–∞–º–∞–Ω—á–∏–≤–æ –±—ã–ª–æ –±—ã –∏—Å–ø–æ–ª—å–∑–æ–≤–∞—Ç—å –≤—Ö–æ–¥ OE, ..... . –ù–æ –≤ —Ä–µ–∞–ª–∏–∑–∞—Ü–∏–∏ diplodok —Ç–∞–∫–æ–π –Ω–æ–º–µ—Ä –Ω–µ –ø—Ä–æ–π–¥–µ—Ç –ø–æ –æ—á–µ–≤–∏–¥–Ω—ã–º –ø—Ä–∏—á–∏–Ω–∞–º: –∫–∞–∫ —Ç–æ–ª—å–∫–æ –≤—Å–µ –≤—ã—Ö–æ–¥—ã –ø–∞–¥–∞—é—Ç –≤ 0, —Å—Ä–∞–±–∞—Ç—ã–≤–∞–µ—Ç –¥–∏–æ–¥–Ω—ã–π "–¥–µ—Ç–µ–∫—Ç–æ—Ä –Ω—É–ª–µ–π" –∏ –∑–∞–ø—É—Å–∫–∞–µ—Ç –Ω–∞ –≤—Ö–æ–¥ —Ä–µ–≥–∏—Å—Ç—Ä–∞ –æ—á–µ—Ä–µ–¥–Ω—É—é –µ–¥–∏–Ω–∏—Ü—É. –ê —ç—Ç–æ –Ω–∞—Å —Å–æ–≤–µ—Ä—à–µ–Ω–Ω–æ –Ω–µ —É—Å—Ç—Ä–∞–∏–≤–∞–µ—Ç... –°–æ—Å—Ç–æ—è–Ω–∏–µ –Ω–∞ –≤—Ö–æ–¥ D —Ä–µ–≥–∏—Å—Ç—Ä–∞ –≤–∞–∂–Ω–æ —Ç–æ–ª—å–∫–æ –≤ –º–æ–º–µ–Ω—Ç –ø–æ–ª–æ–∂–∏—Ç–µ–ª–Ω–æ–≥–æ —Ñ—Ä–æ–Ω—Ç–∞ –Ω–∞ –≤—Ö–æ–¥ CK - —Ç–∞–∫—Ç —Å–¥–≤–∏–≥. —Ä–µ–≥–∏—Å—Ç—Ä–∞. –¢–∞–∫–∏–º –æ–±—Ä–∞–∑–æ–º –µ—Å–ª–∏ –ø–æ—Å–ª–µ —Ñ—Ä–æ–Ω—Ç–∞ –ø—É—Å—Ç–∏–º –Ω–∞ –≤—Ö–æ–¥ –û–ï –∫–æ—Ä–æ—Ç–∫–∏–π –∏–º–ø—É–ª—å—Å —Ç–æ –≤—ã—Ö–æ–¥—ã "—É–π–¥—É—Ç" –≤ Z.  –î–æ–±–∞–≤–ª–µ–Ω–æ C2, R3. U2c, U2d - –æ–Ω–∏ —Ñ–æ—Ä–º–∏—Ä—É—é—Ç –∫–æ—Ä–æ—Ç–∫–∞—è 1 –Ω–∞ –≤—Ö–æ–¥ –û–ï. –û–ø–∞—Å–Ω–æ—Å—Ç—å –≤ —Ç–µ–º, —á—Ç–æ –≤—ã—Ö–æ–¥—ã –ø–µ—Ä–µ–∫–ª—é—á–∞—é—Ç—Å—è –≤ Z —Å–æ—Å—Ç–æ—è–Ω–∏—è. –û—Ç—Å—é–¥–∞ —Å–ª–µ–¥—É–µ—Ç - –ø–æ—Å–ª–µ–¥—É—é—â–∏–µ –∫–∞—Å–∫–∞–¥—ã –¥–æ–ª–∂–Ω—ã –æ–±–µ—Ä–µ–≥–∞—Ç—å —Å–µ–±–µ –æ—Ç –Ω–µ–ø–æ–¥–∫–ª—é—á–µ–Ω–Ω—ã—Ö –≤—Ö–æ–¥–æ–≤. –í –∏–¥–µ–∞–ª–µ - –∫–∞–∂–¥—ã–π –≤—ã—Ö–æ–¥ (Q0-Q6) –¥–æ–ª–∂–µ–Ω –±—ã—Ç—å –ø—Ä–∏—Ç—è–Ω—É—Ç—å –∫ –∑–µ–º–ª–µ —Å–æ–ø—Ä. 10-100–ö PS: –ú–æ–∂–Ω–æ –æ—Ç–∫–∞–∑–∞—Ç—å—Å—è –æ—Ç U2c, U2d. –ù–∞ –≤—Ö–æ–¥ –û–ï –µ—Å—Ç—å –∏–Ω–≤–µ—Ä—Ç–æ—Ä.

|

|

| –í–µ—Ä–Ω—É—Ç—å—Å—è –Ω–∞–≤–µ—Ä—Ö |

|

|

KorbenDallas

|

–ó–∞–≥–æ–ª–æ–≤–æ–∫ —Å–æ–æ–±—â–µ–Ω–∏—è: Re: –ò–Ω–∏—Ü–∏–∞–ª–∏–∑–∏—Ä–æ–≤–∞—Ç—å —Ä–µ–≥–∏—Å—Ç—Ä 74HC595N  –î–æ–±–∞–≤–ª–µ–Ω–æ: –î–æ–±–∞–≤–ª–µ–Ω–æ: –í—Å —Ñ–µ–≤ 14, 2021 20:03:16 |

|

| –í—Å—Ç–∞–ª –Ω–∞ –ª–∞–ø—ã |

|

–ö–∞—Ä–º–∞: 1

–Ý–µ–π—Ç–∏–Ω–≥ —Å–æ–æ–±—â–µ–Ω–∏–π: -1

–ó–∞—Ä–µ–≥–∏—Å—Ç—Ä–∏—Ä–æ–≤–∞–Ω: –ü–Ω –æ–∫—Ç 31, 2016 06:23:19

–°–æ–æ–±—â–µ–Ω–∏–π: 93

–Ý–µ–π—Ç–∏–Ω–≥ —Å–æ–æ–±—â–µ–Ω–∏—è: 0

|

–°–æ—Å—Ç–æ—è–Ω–∏–µ –Ω–∞ –≤—Ö–æ–¥ D —Ä–µ–≥–∏—Å—Ç—Ä–∞ –≤–∞–∂–Ω–æ —Ç–æ–ª—å–∫–æ –≤ –º–æ–º–µ–Ω—Ç –ø–æ–ª–æ–∂–∏—Ç–µ–ª–Ω–æ–≥–æ —Ñ—Ä–æ–Ω—Ç–∞ –Ω–∞ –≤—Ö–æ–¥ CK - —Ç–∞–∫—Ç —Å–¥–≤–∏–≥. —Ä–µ–≥–∏—Å—Ç—Ä–∞. –¢–∞–∫–∏–º –æ–±—Ä–∞–∑–æ–º –µ—Å–ª–∏ –ø–æ—Å–ª–µ —Ñ—Ä–æ–Ω—Ç–∞ –ø—É—Å—Ç–∏–º –Ω–∞ –≤—Ö–æ–¥ –û–ï –∫–æ—Ä–æ—Ç–∫–∏–π –∏–º–ø—É–ª—å—Å —Ç–æ –≤—ã—Ö–æ–¥—ã "—É–π–¥—É—Ç" –≤ Z. –¢–∞–∫ –∞ —á—Ç–æ –≤ —ç—Ç–æ–π —Å—Ö–µ–º–µ –æ–±–µ—Å–ø–µ—á–∏–≤–∞–µ—Ç —Ç–æ, —á—Ç–æ–±—ã –∏–º–ø—É–ª—å—Å –Ω–∞ OE –ø—Ä–∏—à–µ–ª –ø–æ—Å–ª–µ —Ñ—Ä–æ–Ω—Ç–∞? –û—Ç–∫—É–¥–∞ –≤–æ–∑—å–º–µ—Ç—Å—è "–ø–æ—Å–ª–µ"? –ó–∞–¥–µ—Ä–∂–∫–∞ –∏–Ω–≤–µ—Ä—Ç–µ—Ä–∞–º–∏? –ò –µ—Å–ª–∏ –∏–º–ø—É–ª—å—Å –Ω–∞ OE –¥–µ–π—Å—Ç–≤–∏—Ç–µ–ª—å–Ω–æ –ø—Ä–∏–¥–µ—Ç –ø–æ—Å–ª–µ —Ñ—Ä–æ–Ω—Ç–∞, —Ç–æ –≥–¥–µ –≥–∞—Ä–∞–Ω—Ç–∏—è, —á—Ç–æ —Å–æ—Å—Ç–æ—è–Ω–∏–µ Z –Ω–µ "—Ä–∞–∑—Ä—É–±–∏—Ç" —É–∂–µ –ø—Ä–∏—Å—É—Ç—Å—Ç–≤—É—é—â—É—é –µ–¥–∏–Ω–∏—Ü—É –Ω–∞ –æ–¥–Ω–æ–º –∏–∑ –≤—ã—Ö–æ–¥–æ–≤ –Ω–∞ –º–∞–Ω–µ—Ä: 1zzz1111111?

|

|

| –í–µ—Ä–Ω—É—Ç—å—Å—è –Ω–∞–≤–µ—Ä—Ö |

|

|

Novice user

|

–ó–∞–≥–æ–ª–æ–≤–æ–∫ —Å–æ–æ–±—â–µ–Ω–∏—è: Re: –ò–Ω–∏—Ü–∏–∞–ª–∏–∑–∏—Ä–æ–≤–∞—Ç—å —Ä–µ–≥–∏—Å—Ç—Ä 74HC595N  –î–æ–±–∞–≤–ª–µ–Ω–æ: –î–æ–±–∞–≤–ª–µ–Ω–æ: –í—Å —Ñ–µ–≤ 14, 2021 21:22:36 |

|

| –ì–æ–≤–æ—Ä—è—â–∏–π —Å —Ç–µ–∫—Å—Ç–æ–ª–∏—Ç–æ–º |

–ö–∞—Ä–º–∞: 11

–Ý–µ–π—Ç–∏–Ω–≥ —Å–æ–æ–±—â–µ–Ω–∏–π: 94

–ó–∞—Ä–µ–≥–∏—Å—Ç—Ä–∏—Ä–æ–≤–∞–Ω: –í—Ç —è–Ω–≤ 05, 2016 10:14:25

–°–æ–æ–±—â–µ–Ω–∏–π: 1678

–û—Ç–∫—É–¥–∞: –ø–æ—Å–µ–ª–æ–∫ –ú–µ–ª–µ—É–∑

–Ý–µ–π—Ç–∏–Ω–≥ —Å–æ–æ–±—â–µ–Ω–∏—è: 0

|

|

–¥–µ—Å—Å–∞—Ä—Ç–∞—Ü–∏—è –Ω–∞–≤–µ—Ä–Ω–æ,,,

|

|

| –í–µ—Ä–Ω—É—Ç—å—Å—è –Ω–∞–≤–µ—Ä—Ö |

|

|

diplodok

|

–ó–∞–≥–æ–ª–æ–≤–æ–∫ —Å–æ–æ–±—â–µ–Ω–∏—è: Re: –ò–Ω–∏—Ü–∏–∞–ª–∏–∑–∏—Ä–æ–≤–∞—Ç—å —Ä–µ–≥–∏—Å—Ç—Ä 74HC595N  –î–æ–±–∞–≤–ª–µ–Ω–æ: –î–æ–±–∞–≤–ª–µ–Ω–æ: –í—Å —Ñ–µ–≤ 14, 2021 21:30:54 |

|

| –ì–æ–≤–æ—Ä—è—â–∏–π —Å —Ç–µ–∫—Å—Ç–æ–ª–∏—Ç–æ–º |

–ö–∞—Ä–º–∞: 20

–Ý–µ–π—Ç–∏–Ω–≥ —Å–æ–æ–±—â–µ–Ω–∏–π: 513

–ó–∞—Ä–µ–≥–∏—Å—Ç—Ä–∏—Ä–æ–≤–∞–Ω: –ß—Ç –∞–≤–≥ 10, 2017 20:57:51

–°–æ–æ–±—â–µ–Ω–∏–π: 1692

–Ý–µ–π—Ç–∏–Ω–≥ —Å–æ–æ–±—â–µ–Ω–∏—è: 0

|

|

–ö–∞–∫ —Ä–∞–±–æ—Ç–∞–µ—Ç —Å—Ö–µ–º–∞:

1. –ø—Ä–∏ –≤–∫–ª—é—á–µ–Ω–∏–µ C1R2 –æ–±–Ω—É–ª—è—é—Ç —Ä–µ–≥–∏—Å—Ç—Ä

- –Ω–∞ –≤—Ö–æ–¥ D –ø–æ—è–≤–ª—è–µ—Ç—Å—è 1 - —Å —É—Å–ª–æ–≤–∏–µ–º - —á–∏—Ç–∞–π –Ω–∏–∂–µ

2. T–∞–∫—Ç (–≤–æ—Å—Ö–æ–¥—è—â–∏–π —Ñ—Ä–æ–Ω—Ç) "–ø—Ä–∏–Ω–∏–º–∞–µ—Ç" –∏–Ω—Ñ–æ —Å –≤—Ö–æ–¥–∞ D –∏ —Å–¥–≤–∏–≥–∞–µ—Ç —Å–æ–¥–µ—Ä. –≤–ø—Ä–∞–≤–æ

3. –ù–∞ –≤—Ö–æ–¥ –û–ï –ø–æ—è–≤–ª—è–µ—Ç—Å—è –∫–æ—Ä–æ—Ç–∫–∞—è 1. –í—ã—Ö–æ–¥ –≤ Z.

4. –∑–∞–∫–∞–Ω—á–∏–≤–∞–µ–º —Ç–∞–∫—Ç (–ø–∞–¥–∞—é—â–∏–π —Ñ—Ä–æ–Ω—Ç) - –ø–µ—Ä–µ–±—Ä–∞—Å—ã–≤–∞–µ–º –∏–Ω—Ñ–æ —Å —Å–¥–≤–∏–≥–æ–≤–æ–≥–æ —Ä–µ–≥–∏—Å—Ç—Ä–∞ –≤ –≤—ã—Ö–æ–¥–Ω–æ–≥–æ —Ä–µ–≥–∏—Å—Ç—Ä–∞.

5. –§–æ—Ä–º–∏—Ä—É–µ—Ç—Å—è —Å–∏–≥–Ω–∞–ª –¥–ª—è –≤—Ö–æ–¥–∞ D

6.–ø–æ–≤—Ç–æ—Ä—è–µ–º —Å –ø—É–Ω–∫—Ç–∞ 2

–í–∏–¥–∏–º, —á—Ç–æ –Ω–∏–≥–¥–µ –Ω–µ—Ç –∫–æ–ª–∏–∑–∏–π

–¢–∞–∫–∏–º –æ–±—Ä–∞–∑–æ–º –º–æ–µ –≤—ã—Ä–∞–∂–µ–Ω–∏–µ "–ø–æ—Å–ª–µ —Ñ—Ä–æ–Ω—Ç–∞" –Ω–µ –∏–º–µ–µ—Ç —Å–º—ã—Å–ª–∞ - –∏–∑–≤–∏–Ω–∏.

–ù–æ (—É—Å–º–æ—Ç—Ä–µ–ª –¥—Ä—É–≥–æ–µ):

–ü–æ—Å–ª–µ –ø—É–Ω–∫—Ç–∞ 1 –Ω–∞ –≤—ã—Ö–æ–¥–µ –º—ã –º–æ–∂–µ—Ç –ø–æ–ª—É—á–∏—Ç—å —á—Ç–æ —É–≥–æ–¥–Ω–æ (0 –∏–ª–∏ 1). –ú—ã –æ–±–Ω—É–ª—è–µ–º —Ç–æ–ª—å–∫–æ —Å–¥–≤–∏–≥. —Ä–µ–≥–∏—Å—Ç—Ä–∞, –Ω–æ –Ω–µ –∏ –≤—ã—Ö —Ä–µ–≥–∏—Å—Ç—Ä–∞.

–¢–∞–∫–∏–º –æ–±—Ä–∞–∑–æ–º —Å–æ—Å—Ç–æ—è–Ω–∏–µ 10000000 –º–æ–∂–Ω–æ –Ω–µ –ø–æ–ª—É—á–∏—Ç—Å—è –ø–æ—Å–ª–µ –ø–µ—Ä–≤–æ–≥–æ —Ç–∞–∫—Ç–∞. –ú–∞–∫—Å –≤—Ä–µ–º—è —É—Å—Ç–∞–Ω–æ–≤–∫–∏ (–≤ 10000000) –±—É–¥–µ—Ç 2 —Ç–∞–∫—Ç–∞.

PS: –ñ–µ–ª–∞—Ç–µ–ª–Ω–æ —á—Ç–æ–±—ã —Ç–∞–∫—Ç–æ–≤—ã–π –Ω–∞—á–∏–Ω–∞–ª—Å—è —Å –ø–∞–¥–∞—é—â–∏–π (–æ—Ç—Ä–∏—Ü) —Ñ—Ä–æ–Ω—Ç - –ø–µ—Ä–µ–±—Ä–æ—Å–∫–∞ —Å —Å–¥–≤–∏–≥ —Ä–µ–≥ –≤ –≤—ã—Ö. —Ä–µ–≥. –¢–æ–≥–¥–∞ –≤—Å–µ –±—É–¥–µ—Ç –∫–∞–∫ –Ω–∞–¥–æ.

|

|

| –í–µ—Ä–Ω—É—Ç—å—Å—è –Ω–∞–≤–µ—Ä—Ö |

|

|

|

–°—Ç—Ä–∞–Ω–∏—Ü–∞ 1 –∏–∑ 3

|

[ –°–æ–æ–±—â–µ–Ω–∏–π: 42 ] |

, , |

–ö—Ç–æ —Å–µ–π—á–∞—Å –Ω–∞ —Ñ–æ—Ä—É–º–µ |

–°–µ–π—á–∞—Å —ç—Ç–æ—Ç —Ñ–æ—Ä—É–º –ø—Ä–æ—Å–º–∞—Ç—Ä–∏–≤–∞—é—Ç: Popesych –∏ –≥–æ—Å—Ç–∏: 18 |

|

–í—ã –Ω–µ –º–æ–∂–µ—Ç–µ –Ω–∞—á–∏–Ω–∞—Ç—å —Ç–µ–º—ã

–í—ã –Ω–µ –º–æ–∂–µ—Ç–µ –æ—Ç–≤–µ—á–∞—Ç—å –Ω–∞ —Å–æ–æ–±—â–µ–Ω–∏—è

–í—ã –Ω–µ –º–æ–∂–µ—Ç–µ —Ä–µ–¥–∞–∫—Ç–∏—Ä–æ–≤–∞—Ç—å —Å–≤–æ–∏ —Å–æ–æ–±—â–µ–Ω–∏—è

–í—ã –Ω–µ –º–æ–∂–µ—Ç–µ —É–¥–∞–ª—è—Ç—å —Å–≤–æ–∏ —Å–æ–æ–±—â–µ–Ω–∏—è

–í—ã –Ω–µ –º–æ–∂–µ—Ç–µ –¥–æ–±–∞–≤–ª—è—Ç—å –≤–ª–æ–∂–µ–Ω–∏—è

|

|

|