–£ –º–µ–Ω—è –Ω–µ –≤—Å–µ –¥–æ–∫—É–º–µ–Ω—Ç—ã –µ—Å—Ç—å, –∞ –≤ —Ç–µ—Ö, —á—Ç–æ –µ—Å—Ç—å, –ø—Ä—è–º–æ –Ω–µ –≥–æ–≤–æ—Ä–∏—Ç—Å—è –æ —Ä–∞–∑–Ω–æ–º –≤–∫–ª—é—á–µ–Ω–∏–∏, –Ω–æ –µ—Å—Ç—å –¥–æ–≥–∞–¥–∫–∞.

–í —Å–ø—Ä–∞–≤–æ—á–Ω–æ–º –ª–∏—Å—Ç–µ –Ω–∞—à–µ–ª –ø—Ä–∏–º–µ—á–∞–Ω–∏–µ, —á—Ç–æ —Ä–∞–∑—Ä—è–¥–Ω–æ—Å—Ç—å —à–∏–Ω—ã –æ–ø—Ä–µ–¥–µ–ª—è–µ—Ç—Å—è —Å–∏–≥–Ω–∞–ª–æ–º PAGE_EN/SI.

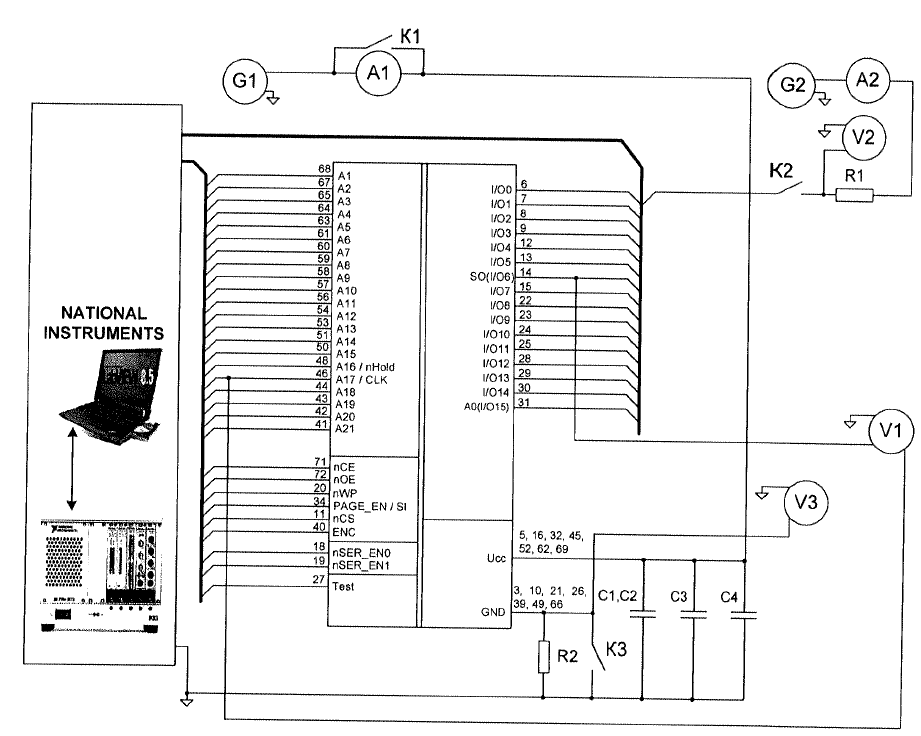

–ê –µ—â–µ —Ç–∞–º —Å—Ä–µ–¥–∏ –ø—Ä–æ—á–µ–≥–æ –µ—Å—Ç—å —Ç–∞–∫–æ–π —Ä–∏—Å—É–Ω–æ–∫:

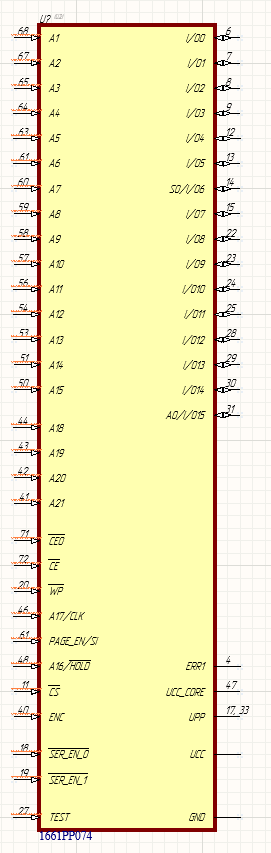

–°–ø–æ–π–ª–µ—Ä

–û–±—â–∞—è –µ–º–∫–æ—Å—Ç—å –º–∏–∫—Ä–æ—Å—Ö–µ–º—ã 16 –ú–±–∏—Ç, –∞–¥—Ä–µ—Å–Ω—ã–π –≤—Ö–æ–¥ –ê21 –∏—Å–ø–æ–ª—å–∑—É–µ—Ç—Å—è —Ç–æ–ª—å–∫–æ –¥–ª—è "—Å—Ç–∞—Ä—à–∏—Ö" –≤–µ—Ä—Å–∏–π –Ω–∞ 32 –ú–±–∏—Ç.

–ï—Å–ª–∏ —Ä–∞–∑–º–µ—Ä —à–∏–Ω—ã 16 –±–∏—Ç, —Ç–æ –ø—Ä–∏ –∏—Å–ø–æ–ª—å–∑–æ–≤–∞–Ω–∏–∏ 20 —Å–≤–æ–±–æ–¥–Ω—ã—Ö –ª–∏–Ω–∏–π –∞–¥—Ä–µ—Å–∞, –Ω–∞—á–∏–Ω–∞—è —Å –ê1, –ø–æ–ª—É—á–∏—Ç—Å—è 2^20 = 1 048 576 –∞–¥—Ä–µ—Å–æ–≤, –ø–æ 16 –±–∏—Ç –∫–∞–∫ —Ä–∞–∑ –±—É–¥–µ—Ç 16 –ú–±–∏—Ç.

–ï—Å–ª–∏ —Ä–∞–∑–º–µ—Ä —à–∏–Ω—ã 8 –±–∏—Ç (–Ω–∞–∏–±–æ–ª–µ–µ –≤–µ—Ä–æ—è—Ç–Ω–æ, —á—Ç–æ –≤—ã–±–æ—Ä —Å –ø–æ–º–æ—â—å—é PAGE_EN –º–µ–∂–¥—É —ç—Ç–∏–º–∏ –¥–≤—É–º—è —Ä–∞–∑–º–µ—Ä–Ω–æ—Å—Ç—è–º–∏), —Ç–æ —Å—Ç–∞—Ä—à–∏–µ 8 –±–∏—Ç –Ω–µ –Ω—É–∂–Ω–æ –∏—Å–ø–æ–ª—å–∑–æ–≤–∞—Ç—å, –∏ –≤—ã–≤–æ–¥ IO15 –Ω–∞—á–∏–Ω–∞–µ—Ç —Ä–∞–±–æ—Ç–∞—Ç—å –∫–∞–∫ –∞–¥—Ä–µ—Å–Ω—ã–π, —Å –æ—Å—Ç–∞–ª—å–Ω—ã–º–∏ –¥–∞–≤–∞—è 2^21 = 2¬Ý097¬Ý152‚Ĩ –∞–¥—Ä–µ—Å–æ–≤, –ø–æ 8 –±–∏—Ç –ø–æ–ª—É—á–∞—Ç—Å—è —Ç–µ –∂–µ 16 –ú–±–∏—Ç.

–í—Ä–æ–¥–µ –ª–æ–≥–∏—á–Ω–æ. –ü—Ä–æ–≤–µ—Ä—é –ø–æ-–∂–∏–≤–æ–º—É)