ąĀą░ą┤ąĖąŠąÜąŠčé >ąĪčéą░čéčīąĖ >

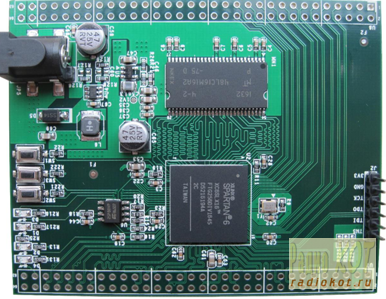

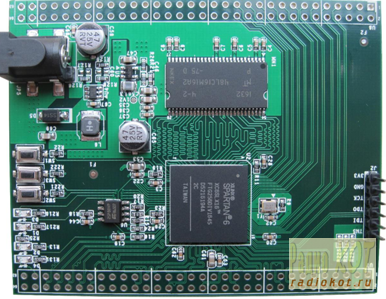

ąĀčāą║ąŠą▓ąŠą┤čüčéą▓ąŠ ą┐ąŠ ą▒čŗčüčéčĆąŠą╝čā čüčéą░čĆčéčā čü ą┐ą╗ą░č鹊ą╣ QMTECH Xilinx SPARTAN-6.

ą¦ą░čüčéčī1. ąĀčāą║ąŠą▓ąŠą┤čüčéą▓ąŠ ą┐ąŠ ą▒čŗčüčéčĆąŠą╝čā čüčéą░čĆčéčā čü ą┐ą╗ą░č鹊ą╣ QMTECH Xilinx SPARTAN-6.

ąöą░ąĮąĮąŠąĄ čĆčāą║ąŠą▓ąŠą┤čüčéą▓ąŠ ąĮąĄ ą┐čĆąĄč鹥ąĮą┤čāąĄčé ąĮą░ ąĮąŠą▓ąĖąĘąĮčā ąĖą╗ąĖ ąŠčĆąĖą│ąĖąĮą░ą╗čīąĮąŠčüčéčī – čģąŠčćčā ą┐ąŠą╝ąŠčćčī ąĮą░čćąĖąĮą░čÄčēąĖą╝ ą▒čŗčüčéčĆąĄąĄ čĆą░ąĘąŠą▒čĆą░čéčīčüčÅ čü ą┐ą╗ą░č鹊ą╣. ą£ąŠąČąĄčé ą│ą┤ąĄ-č鹊 ąĖ ą┐ąŠą▓č鹊čĆčÅčÄčüčī, ąĮąŠ, ą┤čāą╝ą░čÄ, ąĖąĮč乊čĆą╝ą░čåąĖąĖ ą┐ąŠ ą▒čŗčüčéčĆčŗą╝ čüčéą░čĆčéą░ą╝, ąŠčüąŠą▒ąĄąĮąĮąŠ ą┤ą╗čÅ ąĮąŠą▓ąĖčćą║ąŠą▓ ą╝ąĮąŠą│ąŠ ąĮąĄ ą▒čŗą▓ą░ąĄčé.

ąöą╗čÅ ąĮą░čćą░ą╗ą░ ą╝ąŠąČąĮąŠ ą┐čĆąĖąŠą▒čĆąĄčüčéąĖ ą┤ą░ąĮąĮčāčÄ ą┐ą╗ą░čéčā (čÅ ąĮą░ą┐čĆąĖą╝ąĄčĆ ąĘą░ą║ą░ąĘą░ą╗ čü ąÉą╗ąĖ菹║čüą┐čĆąĄčüčü):

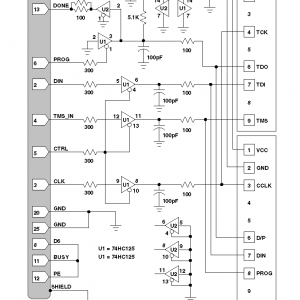

ąÆąĮąĄčłąĮąĖą╣ ą▓ąĖą┤ ąŠčéą╗ą░ą┤ąŠčćąĮąŠą╣ ą┐ą╗ą░čéčŗ:

…ąĖą╝ąĄąĄčé ąĮą░ ą▒ąŠčĆčéčā

1) čĆą░ąĘčŖčæą╝ ą┐ąĖčéą░ąĮąĖčÅ (čÅ ą┐ąŠą┤ą░čÄ 9ąÆ)

2) čüčéą░ą▒ąĖą╗ąĖąĘą░č鹊čĆ

3) 3 ą║ąĮąŠą┐ą║ąĖ (2 ą┐ąŠą╗čīąĘąŠą▓ą░č鹥ą╗čīčüą║ąĖąĄ ąĖ 1 čüąĖčüč鹥ą╝ąĮą░čÅ – ąĘą░ą│čĆčāąĘą║ą░ ą║ąŠąĮčäąĖą│čāčĆą░čåąĖąĖ ąĖąĘ FLASH ą▓ ą¤ąøąśąĪ)

4) 4 čüą▓ąĄč鹊ą┤ąĖąŠą┤ą░ (2 ą┐ąŠą╗čīąĘąŠą▓ą░č鹥ą╗čīčüą║ąĖąĄ, ąĖąĮą┤ąĖą║ą░č鹊čĆ ąĘą░ą│čĆčāąĘą║ąĖ ąĖ ą┐ąĖčéą░ąĮąĖčÅ)

5) ąĀą░ąĘčŖąĄą╝ ą┤ą╗čÅ ą┐ąŠą┤ą║ą╗čÄč湥ąĮąĖčÅ ą┐čĆąŠą│čĆą░ą╝ą╝ą░č鹊čĆą░ ą┐ąŠ JTAG (Platform Cable USB)

6) SPI FLASH ą┤ą╗čÅ čģčĆą░ąĮąĄąĮąĖčÅ ą║ąŠąĮčäąĖą│čāčĆą░čåąĖąĖ

7) SDRAM 32Mb

8) ą×čéą▓ąĄčĆčüčéąĖčÅ ą┤ą╗čÅ ą▓ą┐ą░ą╣ą║ąĖ čĆą░ąĘčŖąĄą╝ąŠą▓ (ą┐ąŠą╗čīąĘąŠą▓ą░č鹥ą╗čīčüą║ąĖąĄ ą▓čģąŠą┤čŗ-ą▓čŗčģąŠą┤čŗ)

9) ąĪą░ą╝ą░ ą¤ąøąśąĪ Xilinx S-6 (ąĮą░ ą║ąŠčĆą┐čāčüąĄ ąŠą▒ąŠąĘąĮą░č湥ąĮąĖąĄ ąæąśąĪ ąĖ čéąĖą┐ ą║ąŠčĆą┐čāčüą░).

ąÆ ą║ąŠą╝ą┐ą╗ąĄą║č鹥 ą┐ąŠčüčéą░ą▓ą║ąĖ ą▒čŗą╗ ąĄčēčæ ą┐čĆąŠą│čĆą░ą╝ą╝ą░č鹊čĆ, ą║ą░ą▒ąĄą╗ąĖ ąĖ ą┤ąĖčüą║ ą¤ą× (čĆąĄą╗ąĖąĘ 13.1). ą¤ąĄčĆą▓ąŠąĄ čćč鹊 ąĮąĄąŠą▒čģąŠą┤ąĖą╝ąŠ čüą┤ąĄą╗ą░čéčī – čāčüčéą░ąĮąŠą▓ąĖčéčī ą¤ą× ąĖ ą┤čĆą░ą╣ą▓ąĄčĆ ą┐čĆąŠą│čĆą░ą╝ą╝ą░č鹊čĆą░. ąØą░ ą┤ąĖčüą║ąĄ ąĄčüčéčī ąĖąĮčüčéčĆčāą║čåąĖąĖ, ą┐čĆąŠčåąĄą┤čāčĆą░ ąĮąĄčüą╗ąŠąČąĮą░čÅ, ąĘą░ąĮąĖą╝ą░ąĄčé 15 ą╝ąĖąĮčāčé.

ą¤čĆąŠčüčīą▒ą░ ą║ ą┐čĆąŠą┤ą░ą▓čåčā ąŠą▒ąĄčüą┐ąĄčćąĖčéčī čäą░ą╣ą╗ą░ą╝ąĖ ąĖ ą╝ą░ąĮčāą░ą╗ą░ą╝ąĖ ąŠč湥ąĮčī ąĘą░čéčÅąĮčāą╗ą░čüčī, ą┐ąŠčŹč鹊ą╝čā čĆąĄčłąĖą╗ ąĮą░ą╣čéąĖ čüą░ą╝. ąĪą║ą░čćąĖą▓ą░ąĄą╝ čäą░ą╣ą╗ QM_XC6SLX16_SDRAM_V02.zip čü ą│ąĖčéčģą░ą▒ą░. ą×ąĮ čüąŠą┤ąĄčƹȹĖčé ą┐čĆąĖą╝ąĄčĆčŗ ą┐čĆąŠąĄą║č鹊ą▓, ąŠą┐ąĖčüą░ąĮąĖčÅ ąæąśąĪ ąĖ čüčģąĄą╝čā čüąŠąĄą┤ąĖąĮąĄąĮąĖą╣ ą║ąŠą╝ą┐ąŠąĮąĄąĮč鹊ą▓ ą┐ą╗ą░čéčŗ. ąŚą░ą▒ąĄą│čā ą▓ą┐ąĄčĆčæą┤: ąĄčüčéčī ą┤ą▓ą░ ą┐ąŠą┐čāą╗čÅčĆąĮčŗčģ čÅąĘčŗą║ą░ ąŠą┐ąĖčüą░ąĮąĖčÅ čüčģąĄą╝ VHDL ąĖ Verilog. ąśą╝ąĄčÅ ąŠą┐čŗčé ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮąĖčÅ ąĮą░ ąĪ Verilog ą╝ąĮąĄ ąŠą║ą░ąĘą░ą╗čüčÅ ą▒ąŠą╗ąĄąĄ ą┐ąŠ ą┤čāčłąĄ ąĖ ą╗ąĄą│č湥 ąŠčüą▓ą░ąĖą▓ą░ąĄčéčüčÅ č湥ą╝ VHDL – ą║ą░čćą░ąĄą╝ ą▓čüčæ, čćč鹊 čüą╝ąŠąČąĄą╝ ąĮą░ą╣čéąĖ ą┐ąŠ Verilog, ąĮčā ąĖ ą┐ąŠ VHDL, ąŠčüąĮąŠą▓ą░ą╝ čåąĖčäčĆąŠą▓ąŠą╣ čüčģąĄą╝ąŠč鹥čģąĮąĖą║ąĖ ą║ąŠąĮąĄčćąĮąŠ č鹊ąČąĄ. ą£čŗ ą▒čāą┤ąĄą╝ čäą░ą║čéąĖč湥čüą║ąĖ ąŠą┐ąĖčüčŗą▓ą░čéčī ą╗ąŠą│ąĖą║čā čĆą░ą▒ąŠčéčŗ čüčģąĄą╝, ą░ ąĮąĄ ą┐ąĖčüą░čéčī ą┐čĆąŠą│čĆą░ą╝ą╝čŗ, ą║ą░ą║ čéą░ą║ąŠą▓čŗąĄ.

ą¤čĆąĖ ą┐ąĄčĆą▓ąŠą╝ ą▓ą║ą╗čÄč湥ąĮąĖąĖ ąĮą░čćąĖąĮą░čÄčé ą╝ąĖą│ą░čéčī čüą▓ąĄč鹊ą┤ąĖąŠą┤čŗ, ąĮą░ąČą░čéąĖąĄ ąĮą░ ą║ąĮąŠą┐ą║ąĖ ąĖąĘą╝ąĄąĮčÅąĄčé čĆąĄąČąĖą╝ ą╝ąĖą│ą░ąĮąĖčÅ. ą¤ąŠą┐čĆąŠą▒čāąĄą╝ čĆą░ąĘąŠą▒čĆą░čéčīčüčÅ čćč鹊 ąČąĄ ą▓ ą¤ąøąśąĪ ąĘą░čłąĖč鹊 (ąĖ ą║ą░ą║ ąĘą░čłąĖą▓ą░čéčī). ąöą╗čÅ ąĮą░čćą░ą╗ą░ čüąŠąĘą┤ą░ą┤ąĖą╝ čĆą░ą▒ąŠčćčāčÄ ą┐ą░ą┐ą║čā, ą▓ ą║ąŠč鹊čĆąŠą╣ ą▒čāą┤čāčé čüąŠčģčĆą░ąĮčÅčéčīčüčÅ ąĮą░čłąĖ ą┐čĆąŠąĄą║čéčŗ. ąĀą░čüą┐ą░ą║ąŠą▓čŗą▓ą░ąĄą╝ ą▓ ąĮąĄčæ ą░čĆčģąĖą▓ (ą┐čĆąĖą╝ąĄčĆčŗ čĆą░ą▒ąŠčéčŗ čü ą║ąĮąŠą┐ą║ą░ą╝ąĖ, ą┤ąĖąŠą┤ą░ą╝ąĖ, ą┐ą░ą╝čÅčéčīčÄ ąĖ ą╝ąĄąĮąĄą┤ąČąĄčĆąŠą╝ čéą░ą║čéąĖčĆąŠą▓ą░ąĮąĖčÅ).

ąŚą░ą┐čāčüą║ą░ąĄą╝ ISE Project Navigator. ąĪąŠąĘą┤ą░čæą╝ ąĮąŠą▓čŗą╣ ą┐čĆąŠąĄą║čé čü čāą║ą░ąĘą░ąĮąĖąĄą╝ čéąĖą┐ą░ ąæąśąĪ ąĖ ą║ąŠčĆą┐čāčüą░ (ąĄčüčéčī ąŠą┐ąĖčüą░ąĮąĖčÅ, ą║ą░ą║ čŹč鹊 ą┤ąĄą╗ą░čéčī). ąØą░ą┐čĆčÅą╝čāčÄ ąĘą░ą│čĆčāąĘąĖčéčī ą│ąŠč鹊ą▓čŗąĄ ą┐čĆąŠąĄą║čéčŗ ąĮąĄ čāą┤ą░ą╗ąŠčüčī – ąŠąĮąĖ ą▒ąŠą╗ąĄąĄ ą┐ąŠąĘą┤ąĮąĄą╣ ą▓ąĄčĆčüąĖąĖ, ą┐ąŠčŹč鹊ą╝čā ąĖą╝ą┐ąŠčĆčéąĖčĆčāąĄą╝ čäą░ą╣ą╗čŗ ą▓čĆčāčćąĮčāčÄ ąĖąĘ ą┐ą░ą┐ą║ąĖ čü čĆą░čüą┐ą░ą║ąŠą▓ą░ąĮąĮčŗą╝ąĖ ą┐čĆąĖą╝ąĄčĆą░ą╝ąĖ. ąóą░ą║ ą┤ą░ąČąĄ ą╗čāčćčłąĄ. ą¤ąŠą║ą░ ąĮąĄ ą▒čāą┤ąĄą╝ ą┤čāą╝ą░čéčī ąŠą▒ ąĖąĄčĆą░čĆčģąĖąĖ ą┐čĆąŠąĄą║čéą░, č鹊ą┐ąŠą▓ąŠą╝ ą╝ąŠą┤čāą╗ąĄ ąĖ čé.ą┤. ąØą░ą╝ ąĮčāąČąĮąŠ čĆą░ąĘąŠą▒čĆą░čéčīčüčÅ čćč鹊 ą▓ąĮčāčéčĆąĖ čüąĄą╣čćą░čü. ąśą╝ą┐ąŠčĆčéąĖčĆčāąĄą╝ .ucf čäą░ą╣ą╗ (ąŠą┐ąĖčüą░ąĮąĖąĄ čüąŠąŠčéą▓ąĄčéčüčéą▓ąĖčÅ ą▓ąĮčāčéčĆąĄąĮąĮąĖčģ čåąĄą┐ąĄą╣ čü ą▓ąĮąĄčłąĮąĖą╝ąĖ ą┐ąŠčĆčéą░ą╝ąĖ ą¤ąøąśąĪ):

//--------------------------------------------------------------------------------------------------------------------------------

//input clock signal

NET "sys_clk" LOC = A10 | IOSTANDARD = LVTTL; // (ąĮąŠąČą║ą░ ąÉ10, čüčéą░ąĮą┤ą░čĆčé ąóąóąø ąĮą░ą┐čĆąĖą╝ąĄčĆ)

//reset signal

NET "sys_rst_n" LOC = R7 | IOSTANDARD = LVTTL; // (ą╝ąŠąČąĮąŠ ąĖ ą┐ąŠą┤čéčÅąČą║čā ą┤ąŠą▒ą░ą▓ąĖčéčī – ą┐ąŠąĘąČąĄ čĆą░ąĘą▒ąĄčĆčæč鹥čüčī čüą░ą╝ąĖ, čŹč鹊 ąĮąĄ čüą╗ąŠąČąĮąŠ)

//led_1 signal

NET "led_1" LOC = T9 | IOSTANDARD = LVTTL;

//led_2 signal

NET "led_2" LOC = R9 | IOSTANDARD = LVTTL;

//key_1 signal

NET "key_1" LOC = T8 | IOSTANDARD = LVTTL;

//--------------------------------------------------------------------------------------------------------------------------------

ąŚą┤ąĄčüčī ą╝čŗ ą▓ąĖą┤ąĖą╝ čüąŠąŠčéą▓ąĄčéčüčéą▓ąĖąĄ čåąĄą┐ąĄą╣ čü 菹╗ąĄą║čéčĆąĖč湥čüą║ąŠą╣ čüčģąĄą╝ąŠą╣, ą┐čĆąĖą▓ąĄą┤čæąĮąĮąŠą╣ ą▓ ąŠą┐ąĖčüą░ąĮąĖąĖ ą┐ą╗ą░čéčŗ. NET “…” ą┐ąŠą┤ą║ą╗čÄčćą░ąĄčéčüčÅ čü ąĮčāąČąĮąŠą╝čā ą▓čŗą▓ąŠą┤čā ą¤ąøąśąĪ. "led_2" ą║ą░ą║ ą▒čŗ ą▒čāą╗ąĄą▓ą░ ą┐ąĄčĆąĄą╝ąĄąĮąĮą░čÅ (ą▓ ą░ąĮą░ą╗ąŠą│ąĖąĖ čü ą▒ąĖč鹊ą╝ ą▓čŗčģąŠą┤ąĮąŠą│ąŠ čĆąĄą│ąĖčüčéčĆą░ ą┐ąŠčĆčéą░ ą║ąŠąĮčéčĆąŠą╗ą╗ąĄčĆą░), ą║ąŠč鹊čĆąŠą╣ ą╝ąŠąČąĮąŠ ą┐čĆąĖčüą▓ąŠąĖčéčī 1 ąĖą╗ąĖ 0, ąĖ č鹊ą│ą┤ą░ ą╝ąŠąČąĮąŠ ąĘą░ąČąĄčćčī ąĖą╗ąĖ ą┐ąŠą│ą░čüąĖčéčī čüą▓ąĄč鹊ą┤ąĖąŠą┤. "key_1" č鹊ąČąĄ, ąĮąŠ «ąĮą░ąŠą▒ąŠčĆąŠčé» - 0 ąĖą╗ąĖ 1 «ą▓ ąĮąĄą╣» čāą║ą░ąĘčŗą▓ą░ąĄčé ąĮą░ ąĮą░ąČą░čéčāčÄ ąĖą╗ąĖ ąĮąĄąĮą░ąČą░čéčāčÄ ą║ąĮąŠą┐ą║čā.

ąöą░ą╗ąĄąĄ ąĖą╝ą┐ąŠčĆčéąĖčĆčāąĄą╝ čäą░ą╣ą╗ ąŠą┐ąĖčüą░ąĮąĖčÅ č鹊ą┐ąŠą▓ąŠą│ąŠ ą╝ąŠą┤čāą╗čÅ (čéąĖą┐ą░ main() – ą┐čĆąŠčüčéąĖč鹥 ąĘą░ č鹥čüąĮčāčÄ ą░ąĮą░ą╗ąŠą│ąĖčÄ čü «ąĪ») čü čĆą░čüčłąĖčĆąĄąĮąĖąĄą╝ .v (Verilog):

//////////////////////////////////////////////////////////////////////////////////

module led_top(

input sys_clk,

input sys_rst_n,

output led_1,

output led_2

);

parameter DLY_CNT = 32'd50000000;

parameter HALF_DLY_CNT = 32'd25000000;

reg r_led;

reg l_led;

reg [31:0]count;

//counter control

always@(posedge sys_clk or negedge sys_rst_n)

begin

if(!sys_rst_n)

begin

count <= 32'd0;

end

else if(count == DLY_CNT)

begin

count <= 32'd0;

end

else

begin

count <= count+32'd1;

end

end

//led output register control

always@(posedge sys_clk or negedge sys_rst_n)

begin

if(!sys_rst_n)

begin

r_led <= 1'b0;

l_led <= 1'b0;

end

else if(count < HALF_DLY_CNT)

begin

r_led <= 1'b1;

l_led <= 1'b0;

end

else

begin

r_led <= 1'b0;

l_led <= 1'b1;

end

end

assign led_1 = r_led;

assign led_2 = l_led;

endmodule

ąĀą░ąĘą▒ąŠčĆ...

ą¤ąĄčĆą▓ąŠąĄ, čćč鹊 ą▒čĆąŠčüą░ąĄčéčüčÅ ą▓ ą│ą╗ą░ąĘą░ – čā ąĮą░čü ąĄčüčéčī ą╝ąŠą┤čāą╗čī čüąŠ ą▓čģąŠą┤ąĮčŗą╝ąĖ ąĖ ą▓čŗčģąŠą┤ąĮčŗą╝ąĖ čüąĖą│ąĮą░ą╗ą░ą╝ąĖ, čüąŠąŠčéą▓ąĄčéčüčéą▓čāčÄčēąĖą╝ąĖ čĆąĄą░ą╗čīąĮčŗą╝ ąĮąŠąČą║ą░ą╝ ą¤ąøąśąĪ - čŹč鹊 čāąČąĄ ą║ąŠąĄ-čćč鹊. ąÆ ą╝ąŠą┤čāą╗čī «ą▓čģąŠą┤ąĖčé» čéą░ą║č鹊ą▓ą░čÅ čćą░čüč鹊čéą░ 50ą£ąōčå, ą║ąĮąŠą┐ą║ą░ čüą▒čĆąŠčüą░, «ą▓čŗčģąŠą┤čÅčé» 2 čüą▓ąĄč鹊ą┤ąĖąŠą┤ą░. ąöą░ą╗ąĄąĄ ąĄčüčéčī 2 ą║ąŠąĮčüčéą░ąĮčéčŗ (ą▓ąŠčé čéčāčé čāąČąĄ ąĮą░ą┤ąŠ ą┐ąŠąŠčéą║čĆčŗą▓ą░čéčī ąŠą┐ąĖčüą░ąĮąĖčÅ ąÆąĄčĆąĖą╗ąŠą│ą░ ąĖ ą┐ą░čĆą░ą╗ą╗ąĄą╗čīąĮąŠ čćąĖčéą░čéčī), 2 ąŠą┤ąĮąŠą▒ąĖčéąĮčŗčģ čĆąĄą│ąĖčüčéčĆą░ (ą║ą░ą║-ą▒čŗ 2 ą╗ąŠą║ą░ą╗čīąĮčŗčģ ą┐ąĄčĆąĄą╝ąĄąĮąĮčŗčģ) ąĖ 1 32-ą▒ąĖčéąĮčŗą╣ čĆąĄą│ąĖčüčéčĆ. 1ą╣ ą▒ą╗ąŠą║ always ąŠą▒čĆą░ąĘčāąĄčé čüč湥čéčćąĖą║-ą┤ąĄą╗ąĖč鹥ą╗čī čéą░ą║č鹊ą▓ąŠą╣ čćą░čüč鹊čéčŗ ą┤ąŠ 1ąōčå (50ą£ą│čå ą┤ąĄą╗čÅčéčüčÅ ąĮą░ 50_000_000). ąóąĄą┐ąĄčĆčī čāąČąĄ ąŠą┐ąĄčĆą░č鹊čĆčŗ if-else ąĖ ąĖčģ čüąŠą┤ąĄčƹȹĖą╝ąŠąĄ ąĮąĄ ą┤ąŠą╗ąČąĮąŠ ą▓čŗąĘčŗą▓ą░čéčī ą▓ąŠą┐čĆąŠčüąŠą▓ – ą╗ąŠą│ąĖą║ą░ čĆą░ą▒ąŠčéčŗ čÅčüąĮą░. ąĪčćąĖčéą░ąĄą╝ ą┤ąŠ 50000000 ą┐ąŠč鹊ą╝ čüą▒čĆą░čüčŗą▓ą░ąĄą╝ ąĖ ąŠą┐čÅčéčī ąĖąĮą║čĆąĄą╝ąĄąĮčé ąĮą░ 1. ąŁč鹊čé ą▒ą╗ąŠą║ čĆą░ą▒ąŠčéą░ąĄčé «ą▓čüąĄą│ą┤ą░» ąĮąĄąĘą░ą▓ąĖčüąĖą╝ąŠ ąŠčé ąŠčüčéą░ą╗čīąĮčŗčģ – ąŠą│čĆąŠą╝ąĮąŠąĄ ąŠčéą╗ąĖčćąĖąĄ ąŠčé ą┐čĆąŠčåąĄčüčüąŠčĆą░ (ą║ą░ą║ ą▒čŗ čéą░ą╣ą╝ąĄčĆ ą£ąÜ, ą║ąŠč鹊čĆčŗą╣ č鹊ąČąĄ čĆą░ą▒ąŠčéą░ąĄčé ąĮąĄąĘą░ą▓ąĖčüąĖą╝ąŠ ąŠčé čÅą┤čĆą░).

ąĪą╗ąĄą┤čāčÄčēąĖą╣ ą▒ą╗ąŠą║ always čāąČąĄ ąŠą┐ąĖčüčŗą▓ą░ąĄčé ą╗ąŠą│ąĖą║čā čĆą░ą▒ąŠčéčŗ ą┤ąĖąŠą┤ąŠą▓ ąĖ čüą▓čÅąĘčī čü ą║ąĮąŠą┐ą║ąŠą╣ – ą║ą░ą║ č鹊ą╗čīą║ąŠ čüč湥čéčćąĖą║ ą┤ąŠčüčćąĖčéą░ąĄčé ą┤ąŠ ą┐ąŠą╗ąŠą▓ąĖąĮčŗ ą┐ąĄčĆąĄą║ą╗čÄčćą░ąĄą╝ ą┤ąĖąŠą┤čŗ ą╝ąĄčüčéą░ą╝ąĖ. ąØą░ąČą░čéąĖąĄ ąĮą░ ą║ąĮąŠą┐ą║čā ą▓čŗąĘčŗą▓ą░ąĄčé čüą▒čĆąŠčü čüč湥čéčćąĖą║ą░ ąĖ ąĘą░čüą▓ąĄčéą║čā ą▓čüąĄčģ ą┤ąĖąŠą┤ąŠą▓ (čéą░ą║ąČąĄ ą┐ą░čĆą░ą╗ą╗ąĄą╗čīąĮčŗą╣ ą┐čĆąŠčåąĄčüčü).

ąŚą┤ąĄčüčī ą┐ąŠą║ą░ čĆąĄą│ąĖčüčéčĆčŗ čüą▓ąĄč鹊ą┤ąĖąŠą┤ąŠą▓ – ą╗ąŠą║ą░ą╗čīąĮčŗąĄ ą┐ąĄčĆąĄą╝ąĄąĮąĮčŗąĄ. ą×ą┐ąĄčĆą░č鹊čĆ Assign ą┐ąŠą┤ą║ą╗čÄčćą░ąĄčé ąĖčģ ą║ čĆąĄą░ą╗čīąĮčŗą╝ ą▓čŗą▓ąŠą┤ą░ą╝ ą¤ąøąśąĪ. ąó.ą║ ąĮą░ą╝ ąĮąĄąŠą▒čģąŠą┤ąĖą╝ąŠ ą┐ąŠą╝ąĮąĖčéčī čüąŠčüč鹊čÅąĮąĖąĄ čüą▓ąĄč鹊ą┤ąĖąŠą┤ą░ (ą│ąŠčĆąĖčé/ąĮąĄą│ąŠčĆąĖčé), čŹčéą░ «ą╗ąŠą║ą░ą╗čīąĮą░čÅ» ą┐ąĄčĆąĄą╝ąĄąĮąĮą░čÅ (čĆąĄą│ąĖčüčéčĆ) ąĄčüčéčī čÅč湥ą╣ą║ą░ ą┐ą░ą╝čÅčéąĖ – čéčĆąĖą│ą│ąĄčĆ. ąÜ ąĮąĄą╝čā ąĖ ą┐ąŠą┤ą║ą╗čÄčćą░ąĄą╝ čüą▓ąĄč鹊ą┤ąĖąŠą┤čŗ.

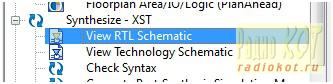

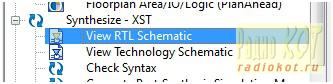

ąÆąŠčé ąĖ čĆą░ąĘąŠą▒čĆą░ą╗ąĖčüčī – ąĮąŠ ą╗čāčćčłąĄąĄ čüčĆąĄą┤čüčéą▓ąŠ ąĖąĘčāč湥ąĮąĖčÅ čÅąĘčŗą║ą░ čŹč鹊 ąŠą▒čēąĄąĮąĖąĄ ąĮą░ ąĮčæą╝, ą┐ąŠčŹč鹊ą╝čā ąĮą░čćąĖąĮą░ąĄą╝ 菹║čüą┐ąĄčĆąĖą╝ąĄąĮčéąĖčĆąŠą▓ą░čéčī. ą¢ą╝ąĄą╝

«Implement Top Module» - čéčĆą░ąĮčüą╗ąĖčĆčāąĄą╝ ąĮą░čłąĄ ąŠą┐ąĖčüą░ąĮąĖąĄ ą▓ čĆąĄą░ą╗čīąĮčāčÄ čüčģąĄą╝čā. ąØąĄ ą┐ąŠą╝ąĮčÄ, ąĮąŠ, ą▓čĆąŠą┤ąĄ ąŠčłąĖą▒ąŠą║ ąĮąĄ ą▒čŗą╗ąŠ ąĖ čÅ čāą▓ąĖą┤ąĄą╗ čüčģąĄą╝čā čāčüčéčĆąŠą╣čüčéą▓ą░...

ąĮą░ čĆąĄą│ąĖčüčéčĆąŠą▓ąŠą╝ čāčĆąŠą▓ąĮąĄ, ą║ą╗ąĖą║ ą┐ąŠ ą┐ąŠčÅą▓ąĖą▓čłąĄą╣čüčÅ čüčģąĄą╝ąĄ čāąČąĄ ą┐ąŠą║ą░ąČąĄčé «ą▓ąĮčāčéčĆąĄąĮąĮąŠčüčéąĖ» - ąŠč湥ąĮčī ą║čĆą░čüąĖą▓ąŠ…čŹč鹊 ą┐ąŠą║ą░ (ą┐ąŠč鹊ą╝ ąĮą░čćąĮąĄčéčüčÅ č湥čĆč鹊ą▓čēąĖąĮą░, ą▓ ąŠčüąĮąŠą▓ąĮąŠą╝ ąĖąĘ-ąĘą░ ąĮąĄą┐čĆą░ą▓ąĖą╗čīąĮąŠą│ąŠ, ąĮąŠ ą▓ą┐ąŠą╗ąĮąĄ čéčĆą░ąĮčüą╗ąĖčĆčāąĄą╝ąŠą│ąŠ ąŠą┐ąĖčüą░ąĮąĖčÅ). ą¢ą╝ąĄą╝

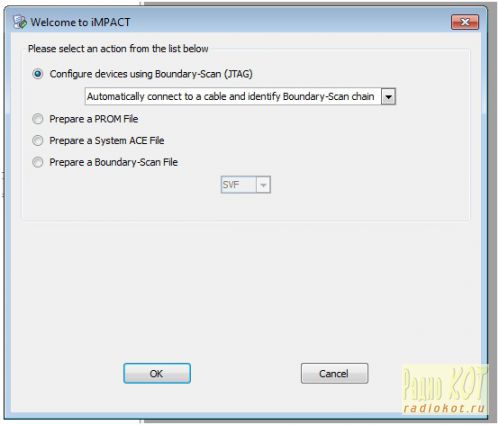

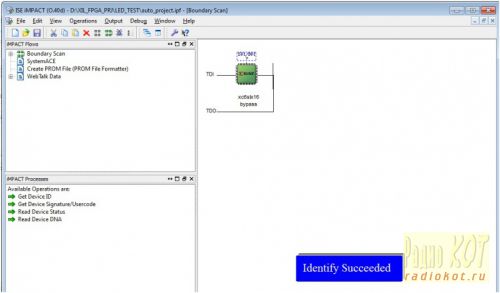

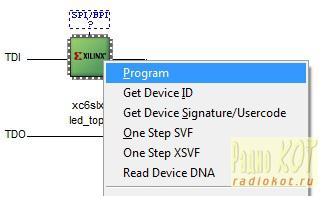

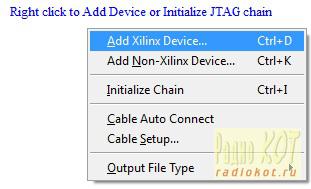

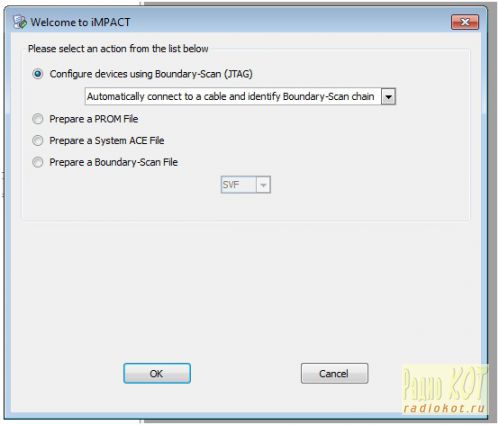

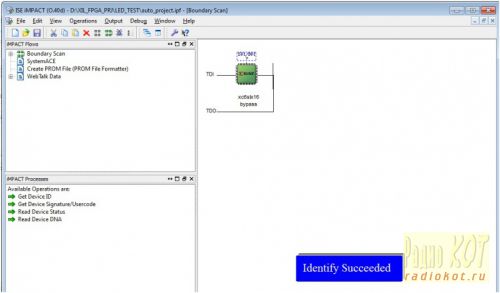

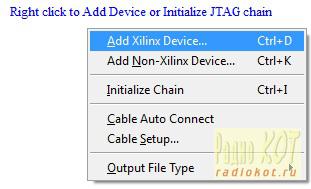

ąĖ ą┐ąŠą╗čāčćąĖą╝ čäą░ą╣ą╗ «ą┐čĆąŠčłąĖą▓ą║ąĖ» ą¤ąøąśąĪ *.bit. ąŚą░ą┐čāčüą║ą░ąĄą╝ čāčéąĖą╗ąĖčéčā iMPACT, čüąŠąĘą┤ą░čæą╝ ą┐čĆąŠąĄą║čé (čāą▒ąĄąČą┤ą░ąĄą╝čüčÅ, čćč鹊 ą┐čĆąŠą│čĆą░ą╝ą╝ą░č鹊čĆ ą┐ąŠą┤ą║ą╗čÄč湥ąĮ, ąĖąĮą┤ąĖą║ą░č鹊čĆ ąĘąĄą╗čæąĮčŗą╣), ą┐ąŠą┤ą║ą╗čÄčćą░ąĄą╝čüčÅ č湥čĆąĄąĘ JTAG:

ąÆąĖą┤ąĖą╝ ą¤ąøąśąĪ.

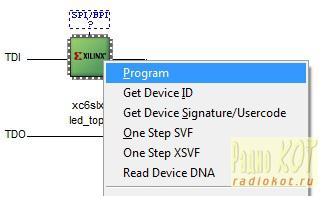

ą×čéą║čĆčŗą▓ą░ąĄą╝ čäą░ą╣ą╗ .bit ą║ąŠąĮčäąĖą│čāčĆą░čåąĖąĖ ąĖ ą▓ ą┐čĆąĖąĮčåąĖą┐ąĄ ą│ąŠč鹊ą▓ąŠ. ą£čŗ č鹥ą┐ąĄčĆčī ą╝ąŠąČąĄą╝ ą┐čĆąŠčłąĖčéčī ą┐ą░ą╝čÅčéčī čüą░ą╝ąŠą╣ ą¤ąøąśąĪ ąĖčüą┐ąŠą╗čīąĘčāčÅ ąĮą░čł .bit čäą░ą╣ą╗, ąĮąŠ ą┐čĆąĖ ą┐ąĄčĆąĄąĘą░ą│čĆčāąĘą║ąĄ ąĖą╗ąĖ ąŠčéą║ą╗čÄč湥ąĮąĖąĖ ą┐ąĖčéą░ąĮąĖčÅ ą┐čĆąŠčłąĖą▓ą║ą░ «čüą╗ąĄčéąĖčé» ąĖ ą¤ąøąśąĪ ąĘą░ą│čĆčāąĘąĖčéčüčÅ čü SPI FLASH ą┐ą░ą╝čÅčéąĖ (ą║ąŠč鹊čĆčāčÄ ą╝čŗ ąĖ ą┐čĆąŠą│čĆą░ą╝ą╝ą░č鹊čĆ ą▓ąĖą┤ąĖą╝ ą┐ąŠą┤ą║ą╗čÄč湥ąĮąĮąŠą╣ ą║ ą¤ąøąśąĪ). ąöą╗čÅ čāčüą║ąŠčĆąĄąĮąĖčÅ ą┐čĆąŠčłąĖą▓ą║ąĖ ąĖ 菹║čüą┐ąĄčĆąĖą╝ąĄąĮč鹊ą▓ ąĮą░ą╝ ą┐ąŠą║ą░ ą┤ąŠčüčéą░č鹊čćąĮąŠ ą│čĆčāąĘąĖčéčī ą║ąŠąĮčäąĖą│čāčĆą░čåąĖčÄ ą▓ čüą░ą╝čā ą¤ąøąśąĪ. ą¤čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░čéčī SPI FLASH ąĮąĄą╝ąĮąŠą│ąŠ čüą╗ąŠąČąĮąĄąĄ ąĖ ą┤ąŠą╗čīčłąĄ, ąĮąŠ čéčāčé čāąČąĄ čĆą░ąĘą▒ąĄčĆčæč鹥čüčī čüą░ą╝ąĖ, ą╝ąĄč鹊ą┤ąŠą╝ ą┐čĆąŠą▒ ąĖ ąŠčłąĖą▒ąŠą║ ąĖą╗ąĖ, ą╗čāčćčłąĄ, ą┐ąŠčćąĖčéą░ą▓ ą╝ą░ąĮčāą░ą╗.

ą¤čĆą░ą▓čŗą╝ ą║ą╗ąĖą║ąŠą╝ ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆčāąĄą╝ ą¤ąøąśąĪ ą╝ąĄąĮąĄąĄ č湥ą╝ ąĘą░ ą┐ąŠą╗čüąĄą║čāąĮą┤čŗ, ąĖ ą┐ąŠą╗čāčćą░ąĄą╝ č鹊čé-ąČąĄ čĆąĄąĘčāą╗čīčéą░čé, čćč鹊 ąĖ ą┤ąŠ ą┐ąĄčĆąĄą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆąŠą▓ą░ąĮąĖčÅ – ąĘąĮą░čćąĖčé ą▓čüčæ ą▓ąĄčĆąĮąŠ.

ąöąĄą╗ą░ąĄą╝, ąĮą░ą┐čĆąĖą╝ąĄčĆ, ą║ąŠąĮčüčéą░ąĮčéčŗ ą▓ 2 čĆą░ąĘą░ ą╝ąĄąĮčīčłąĄ, ą║ąŠą╝ą┐ąĖą╗ąĖčĆčāąĄą╝, ą│ąŠč鹊ą▓ąĖą╝ čäą░ą╣ą╗ ą┐čĆąŠčłąĖą▓ą║ąĖ. ąĪčģąĄą╝ą░ ą┐čĆąĖ čŹč鹊ą╝ ą┐ąŠčćčéąĖ ąĮąĄ ąĖąĘą╝ąĄąĮąĖą╗ą░čüčī.

ąŻą┤ą░ą╗čÅąĄą╝ ąĮą░čłčā ą¤ąøąśąĪ «Del»ąŠą╝, ą┤ąŠą▒ą░ą▓ą╗čÅąĄą╝ ąŠą┐čÅčéčī - čŹč鹊 ąĮąĄ čüąŠą▓čüąĄą╝ ą▓ąĄčĆąĮčŗą╣ ą┐čāčéčī, ąĮąŠ čĆą░ą▒ąŠčéą░ąĄčé:

ąś čüąĮąŠą▓ą░ ą┐čĆąŠą│čĆą░ą╝ą╝ąĖčĆčāąĄą╝, ą┐ąŠą╗čāčćą░ąĄą╝ ą╝ąĖą│ą░ąĮąĖąĄ ą▓ 2 čĆą░ąĘą░ ą▒čŗčüčéčĆąĄąĄ...

ą¤čĆąĖą╝ąĄčĆ ą┐čĆąŠčüč鹊ą╣, ąĮąŠ čāąČąĄ ą┐čĆąĖąŠčéą║čĆčŗčéą░ ąĘą░ą▓ąĄčüą░ čéą░ą╣ąĮčŗ ą¤ąøąśąĪ, ąĖąĘ-ąĘą░ ąĮąĄčæ čüą▓ąĄčéąĖčé ą╗čāčćąĖą║ čéčŗčüčÅčć ą╝ąŠčĆą│ą░čÄčēąĖčģ čüą▓ąĄč鹊ą┤ąĖąŠą┤ąŠą▓ ąĮą░ č鹥čĆąĮąĖčüčéčŗą╣ ą┐čāčéčī ą║ ą▓ąĄčĆčłąĖąĮąĄ ą│ąŠčĆčŗ))) . ąóąĄą┐ąĄčĆčī ąĮą░čćąĖąĮą░ąĄą╝ čāąČąĄ ą▓ą┤čāą╝čćąĖą▓ąŠ čćąĖčéą░čéčī ąŠą┐ąĖčüą░ąĮąĖąĄ čÅąĘčŗą║ą░, čüčéą░ąĮą┤ą░čĆčé ąĮą░ ąÆąĄčĆąĖą╗ąŠą│, čüą╝ąŠčéčĆąĖą╝ ąĖ ą┐čĆąĖą╝ąĄčĆčŗ čüčéą░ąĮą┤ą░čĆčéąĮčŗčģ ąŠą┐ąĖčüą░ąĮąĖą╣ ą╗ąŠą│ąĖč湥čüą║ąĖčģ 菹╗ąĄą╝ąĄąĮč鹊ą▓, čĆąĄą│ąĖčüčéčĆąŠą▓, čüčāą╝ą╝ą░č鹊čĆąŠą▓ ąĖ čĆą░ąĘą▒ąĖčĆą░ąĄą╝ ą║ą░ą║ ąŠąĮąĖ čĆą░ą▒ąŠčéą░čÄčé.

ąĢčüą╗ąĖ čüčéą░čéčīčÅ ą┐ąŠąĮčĆą░ą▓ąĖą╗ą░čüčī, ą┤ą░ą╗ąĄąĄ ą┐ąŠą┤ąĄą╗čÄčüčī ąŠą┐čŗč鹊ą╝ ą┐ąŠą┤ą║ą╗čÄč湥ąĮąĖčÅ čüčéą░ąĮą┤ą░čĆčéąĮčŗčģ ą▒ąĖą▒ą╗ąĖąŠč鹥čćąĮčŗčģ ą╝ąŠą┤čāą╗ąĄą╣ – ąĮą░ą┐čĆąĖą╝ąĄčĆ ą▒čāč乥čĆąŠą▓ ąÆ/ąÆ, ą╝čāą╗čīčéąĖą┐ą╗ąĄą║čüąŠčĆąŠą▓ ąĖ ą╝ąĄąĮąĄą┤ąČąĄčĆą░ čéą░ą║čéąĖčĆąŠą▓ą░ąĮąĖčÅ (ąĮą░ čćą░čüč鹊č鹥 ą▓ 50ą£ąōčå ą┤ą╗čÅ ąĮąĄą║ąŠč鹊čĆčŗčģ ą┐čĆąĖą╝ąĄąĮąĄąĮąĖą╣ ąŠčüąŠą▒ąŠ ąĮąĄ čĆą░ąĘą│ąŠąĮąĖčłčīčüčÅ - ą¤ąøąśąĪ ą▓ ą┐čĆąĖąĮčåąĖą┐ąĄ ąĖ čüąŠąĘą┤ą░ąĮą░ ą┤ą╗čÅ ą▒ąŠą╗čīčłąĖčģ čüą║ąŠčĆąŠčüč鹥ą╣ čĆą░ą▒ąŠčéčŗ ą╝ąĮąŠą│ąĖčģ ą┐ą░čĆą░ą╗ą╗ąĄą╗čīąĮčŗčģ ą┐čĆąŠčåąĄčüčüąŠą▓). ąóą░ą║ąČąĄ ąĮąĄą╗ąĖčłąĮąĄą╣ ą▒čāą┤ąĄčé ąĖ čüąĖą╝čāą╗čÅčåąĖčÅ čüąŠąĘą┤ą░ąĮąĮčŗčģ čüčģąĄą╝ – ą┐čĆąŠčłąĖą▓ą░čéčī ą¤ąøąśąĪ (ąĄčæ ą║ąŠąĮčäąĖą│čāčĆą░čåąĖąŠąĮąĮčāčÄ RAM ) ą╝ąŠąČąĮąŠ ąĮąĄąŠą│čĆą░ąĮąĖč湥ąĮąĮąŠ, ąĮąŠ ą▓čüąĄ-čéą░ą║ąĖ ą╗čāčćčłąĄ čüąĮą░čćą░ą╗ą░ ą┐čĆąŠą▓ąĄčĆąĖčéčī čĆą░ą▒ąŠč鹊čüą┐ąŠčüąŠą▒ąĮąŠčüčéčī ąĮą░ čüąĖą╝čāą╗čÅč鹊čĆąĄ.

ążą░ą╣ą╗čŗ:

ążąŠč鹊ą│čĆą░čäąĖčÅ

ążąŠč鹊ą│čĆą░čäąĖčÅ

ąÆčüąĄ ą▓ąŠą┐čĆąŠčüčŗ ą▓

ążąŠčĆčāą╝.

|

ąÜą░ą║ ą▓ą░ą╝ čŹčéą░ čüčéą░čéčīčÅ?

|

ąŚą░čĆą░ą▒ąŠčéą░ą╗ąŠ ą╗ąĖ čŹč鹊 čāčüčéčĆąŠą╣čüčéą▓ąŠ čā ą▓ą░čü?

|

|

|

|

ąŁčéąĖ čüčéą░čéčīąĖ ą▓ą░ą╝ č鹊ąČąĄ ą╝ąŠą│čāčé ą┐čĆąĖą│ąŠą┤ąĖčéčīčüčÅ: